Trường Sơn

Writer

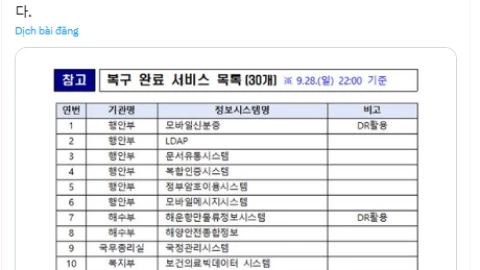

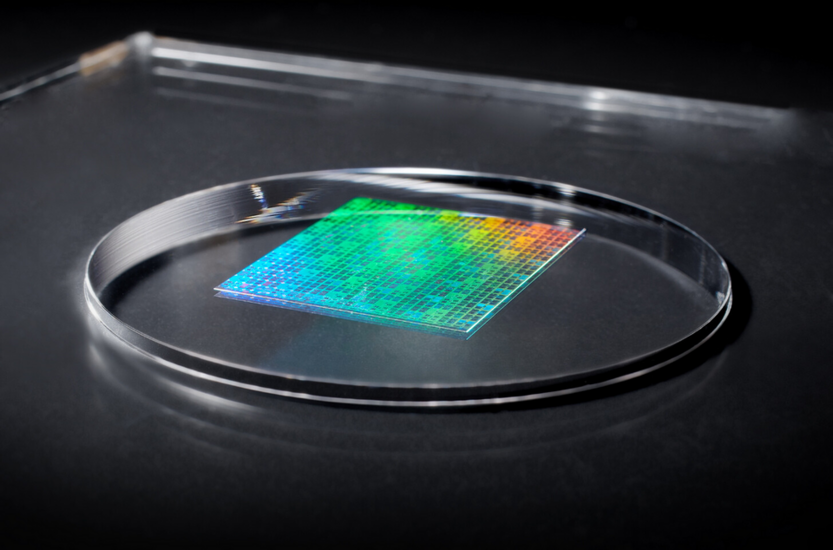

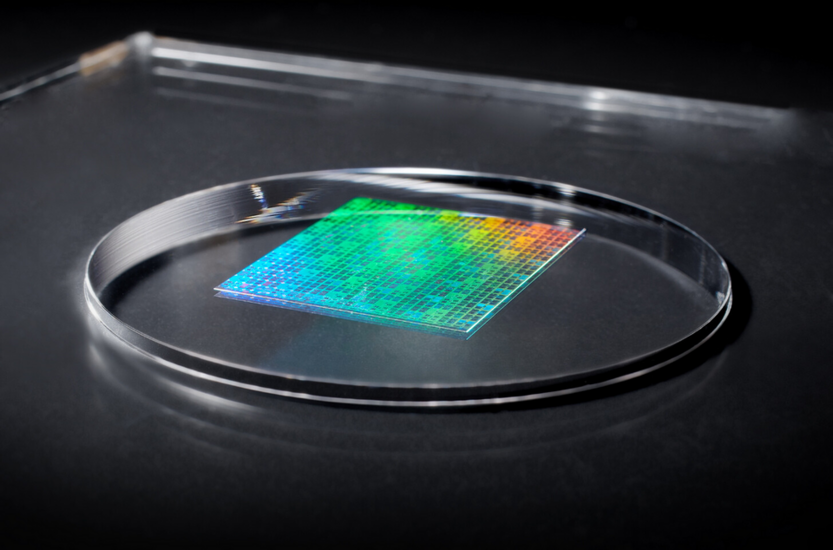

Công ty DNP Corporation của Nhật mới đây đã công bố phát triển thành công khuôn mẫu in nano với độ rộng đường kẻ chỉ 10nm. Khuôn mẫu này có thể được sử dụng để tạo hình các mạch bán dẫn logic ở mức 1,4nm, đáp ứng các yêu cầu thu nhỏ của các chất bán dẫn logic tiên tiến được sử dụng trong các thiết bị như điện thoại thông minh, trung tâm dữ liệu và bộ nhớ flash NAND. Sản phẩm sẽ được trưng bày tại SEMICON Japan 2025, diễn ra tại Tokyo Big Sight từ ngày 17 đến 19 tháng 12 năm 2025.

Trong những năm gần đây, với sự gia tăng liên tục nhu cầu toàn cầu về sức mạnh tính toán, nhu cầu thu nhỏ các chất bán dẫn tiên tiến cũng tăng lên, thúc đẩy sự phát triển không ngừng của sản xuất chip dựa trên công nghệ khắc quang cực tím (EUV). Tuy nhiên, do chi phí cao của thiết bị khắc quang EUV (lên đến 150 triệu đô la Mỹ/đơn vị), chi phí xây dựng dây chuyền sản xuất thậm chí còn cao hơn, và mức tiêu thụ năng lượng của quá trình chiếu xạ cũng rất lớn. Do đó, cần có những giải pháp cấp thiết để giảm chi phí sản xuất và giảm thiểu tác động đến môi trường.

Do đó, Canon, một nhà sản xuất Nhật Bản đã thất bại trước ASML trên thị trường máy in thạch bản, đã hợp tác với Dai Nippon Printing Co., Ltd. (DNP), một nhà sản xuất linh kiện bán dẫn của Nhật Bản như mặt nạ quang khắc, để phát triển công nghệ in nano trong hơn một thập kỷ.

Công nghệ in nano, hay còn gọi là kỹ thuật in nano, không chuyển cấu trúc vi mô của mạch tích hợp lên tấm silicon bằng phương pháp chiếu ảnh quang học truyền thống. Thay vào đó, nó tương tự như công nghệ in ấn, trực tiếp tạo ra các hoa văn thông qua quá trình in. Bằng cách chỉ in một lần lên tấm wafer, các hoa văn mạch 2D hoặc 3D phức tạp có thể được tạo ra ở những vị trí cụ thể. Điều này không chỉ cực kỳ tiện lợi mà còn cho phép thực hiện công nghệ xử lý 5nm mà không cần đến máy in thạch bản EUV, đồng thời giảm đáng kể chi phí mua sắm thiết bị và sản xuất chip.

Vào tháng 10 năm 2023, Canon chính thức ra mắt thiết bị sản xuất chip FPA-1200NZ2C dựa trên công nghệ nanoimprint (NIL), mở ra một hướng đi mới, tiết kiệm chi phí hơn để sản xuất các chip xử lý tiên tiến.

Theo Canon, thiết bị in nano của hãng có thể hỗ trợ sản xuất các quy trình tiên tiến dưới 10nm, thậm chí lên đến 5nm. So với công nghệ in thạch bản EUV hiện đang được thương mại hóa, mặc dù in nano chậm hơn so với in thạch bản truyền thống, nhưng nó có thể giảm đáng kể mức tiêu thụ năng lượng trong sản xuất chip khoảng 90%, và chi phí mua thiết bị cũng có thể giảm 90%. Giám đốc điều hành của Canon, Fujio Mitarai, trước đây đã chỉ ra rằng giá của thiết bị in nano của Canon sẽ "thấp hơn một bậc so với máy in thạch bản EUV của ASML (tức là chỉ 10%)."

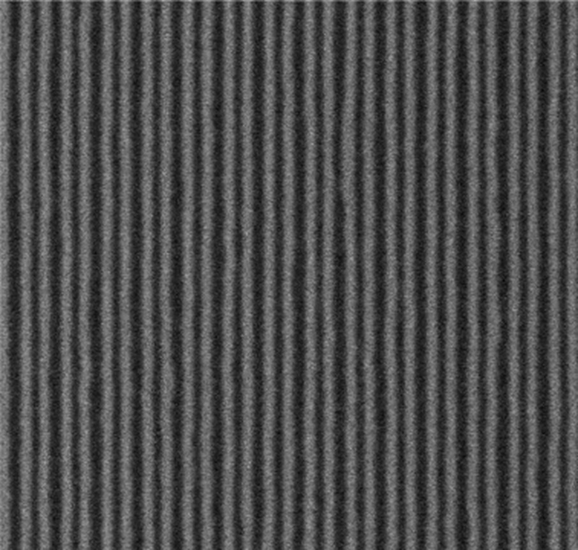

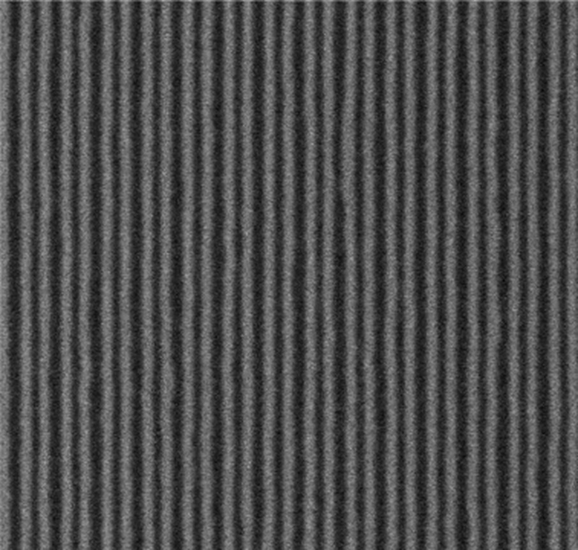

Trên mặt nạ in nano DNP, các đường kẻ có độ rộng 10nm.

Tuy nhiên, ngay cả như vậy, công nghệ in nano vẫn có khả năng cạnh tranh tương đối hạn chế so với công nghệ in EUV đã hoàn thiện của ASML. Nhưng khi công nghệ xử lý tiến bộ đến cấp độ angstrom, thiết bị in EUV có khẩu độ số cao (High NA) của ASML sẽ dẫn đến chi phí sản xuất cao hơn. Nếu công nghệ in nano cũng có thể tiến bộ đến cấp độ angstrom, khả năng cạnh tranh của nó chắc chắn sẽ trở nên nổi bật hơn nữa.

Đối với công nghệ in nano, mức độ hiệu quả của quy trình sản xuất bán dẫn có thể đạt được phụ thuộc trực tiếp vào khuôn mẫu in nano. Không giống như phương pháp chiếu sáng quang học có thể phóng đại nhiều lần, công nghệ in nano yêu cầu ghi "khuôn mẫu chính → khuôn mẫu phụ → khuôn mẫu làm việc" ở tỷ lệ 1:1, và các lỗi có thể xảy ra ở mỗi bước. Đối với kích thước chi tiết dưới 20nm, nó đòi hỏi sự hỗ trợ của máy ghi chùm tia điện tử đa tia (MBMW) hiện đại, và độ khó sản xuất, chi phí và áp lực về năng suất sẽ rất đáng kể đối với các kích thước chi tiết ngày càng lớn hơn.

Từ năm 2003, DNP đã tập trung vào việc phát triển các khuôn mẫu in nano (NIL), giúp giảm tiêu thụ năng lượng trong quá trình chiếu xạ bằng cách in trực tiếp và chuyển các khuôn mẫu có họa tiết mạch được khắc lên chất nền, và đã tích lũy được bí quyết kỹ thuật độc đáo.

DNP vừa công bố phát triển thành công khuôn mẫu in nano (NIL) có độ rộng đường kẻ 10nm, tương đương với quy trình 1,4nm hiện tại, có thể thay thế một số quy trình EUV và thậm chí cả quy trình EUV khẩu độ lớn (High NA) để sản xuất các chất bán dẫn logic tiên tiến, đáp ứng nhu cầu kiểm soát chi phí của khách hàng. Bằng việc cung cấp khuôn mẫu này, DNP sẽ mở rộng sự lựa chọn quy trình sản xuất chất bán dẫn cho khách hàng, từ đó giảm chi phí sản xuất và giảm thiểu tác động đến môi trường.

Theo các báo cáo, DNP sử dụng kỹ thuật tạo mẫu kép tự căn chỉnh (SADP) để thu nhỏ kích thước khuôn mẫu in nano với độ rộng đường kẻ là 10 nm. Công nghệ này tăng gấp đôi mật độ mẫu bằng cách lắng đọng và khắc các lớp màng mỏng trên các mẫu được tạo ra bởi hệ thống in thạch bản.

DNP chỉ ra rằng "quy trình tiết kiệm năng lượng bán dẫn siêu mịn sử dụng công nghệ in thạch bản nano" giúp giảm mức tiêu thụ điện năng xuống còn khoảng một phần mười so với các quy trình chiếu xạ truyền thống (như ArF/DUV ngâm, EUV).

Hiện tại, DNP đang liên hệ với các nhà sản xuất chất bán dẫn và các khách hàng khác, đồng thời đã bắt đầu đánh giá các khuôn mẫu in nano (NIL) với mục tiêu bắt đầu sản xuất hàng loạt vào năm 2027.

Nhìn về phía trước, để tiếp tục đạt được mục tiêu thu nhỏ bán dẫn và giảm chi phí, DNP tuyên bố sẽ tiếp tục thúc đẩy phát triển hơn nữa các khuôn mẫu NIL và tăng cường hệ thống sản xuất để đáp ứng nhu cầu ngày càng tăng, với mục tiêu tăng doanh thu NIL thêm 4 tỷ yên vào năm tài chính 2030.

Nguồn: Chip Intelligence

Trong những năm gần đây, với sự gia tăng liên tục nhu cầu toàn cầu về sức mạnh tính toán, nhu cầu thu nhỏ các chất bán dẫn tiên tiến cũng tăng lên, thúc đẩy sự phát triển không ngừng của sản xuất chip dựa trên công nghệ khắc quang cực tím (EUV). Tuy nhiên, do chi phí cao của thiết bị khắc quang EUV (lên đến 150 triệu đô la Mỹ/đơn vị), chi phí xây dựng dây chuyền sản xuất thậm chí còn cao hơn, và mức tiêu thụ năng lượng của quá trình chiếu xạ cũng rất lớn. Do đó, cần có những giải pháp cấp thiết để giảm chi phí sản xuất và giảm thiểu tác động đến môi trường.

Do đó, Canon, một nhà sản xuất Nhật Bản đã thất bại trước ASML trên thị trường máy in thạch bản, đã hợp tác với Dai Nippon Printing Co., Ltd. (DNP), một nhà sản xuất linh kiện bán dẫn của Nhật Bản như mặt nạ quang khắc, để phát triển công nghệ in nano trong hơn một thập kỷ.

Công nghệ in nano, hay còn gọi là kỹ thuật in nano, không chuyển cấu trúc vi mô của mạch tích hợp lên tấm silicon bằng phương pháp chiếu ảnh quang học truyền thống. Thay vào đó, nó tương tự như công nghệ in ấn, trực tiếp tạo ra các hoa văn thông qua quá trình in. Bằng cách chỉ in một lần lên tấm wafer, các hoa văn mạch 2D hoặc 3D phức tạp có thể được tạo ra ở những vị trí cụ thể. Điều này không chỉ cực kỳ tiện lợi mà còn cho phép thực hiện công nghệ xử lý 5nm mà không cần đến máy in thạch bản EUV, đồng thời giảm đáng kể chi phí mua sắm thiết bị và sản xuất chip.

Vào tháng 10 năm 2023, Canon chính thức ra mắt thiết bị sản xuất chip FPA-1200NZ2C dựa trên công nghệ nanoimprint (NIL), mở ra một hướng đi mới, tiết kiệm chi phí hơn để sản xuất các chip xử lý tiên tiến.

Theo Canon, thiết bị in nano của hãng có thể hỗ trợ sản xuất các quy trình tiên tiến dưới 10nm, thậm chí lên đến 5nm. So với công nghệ in thạch bản EUV hiện đang được thương mại hóa, mặc dù in nano chậm hơn so với in thạch bản truyền thống, nhưng nó có thể giảm đáng kể mức tiêu thụ năng lượng trong sản xuất chip khoảng 90%, và chi phí mua thiết bị cũng có thể giảm 90%. Giám đốc điều hành của Canon, Fujio Mitarai, trước đây đã chỉ ra rằng giá của thiết bị in nano của Canon sẽ "thấp hơn một bậc so với máy in thạch bản EUV của ASML (tức là chỉ 10%)."

Trên mặt nạ in nano DNP, các đường kẻ có độ rộng 10nm.

Tuy nhiên, ngay cả như vậy, công nghệ in nano vẫn có khả năng cạnh tranh tương đối hạn chế so với công nghệ in EUV đã hoàn thiện của ASML. Nhưng khi công nghệ xử lý tiến bộ đến cấp độ angstrom, thiết bị in EUV có khẩu độ số cao (High NA) của ASML sẽ dẫn đến chi phí sản xuất cao hơn. Nếu công nghệ in nano cũng có thể tiến bộ đến cấp độ angstrom, khả năng cạnh tranh của nó chắc chắn sẽ trở nên nổi bật hơn nữa.

Đối với công nghệ in nano, mức độ hiệu quả của quy trình sản xuất bán dẫn có thể đạt được phụ thuộc trực tiếp vào khuôn mẫu in nano. Không giống như phương pháp chiếu sáng quang học có thể phóng đại nhiều lần, công nghệ in nano yêu cầu ghi "khuôn mẫu chính → khuôn mẫu phụ → khuôn mẫu làm việc" ở tỷ lệ 1:1, và các lỗi có thể xảy ra ở mỗi bước. Đối với kích thước chi tiết dưới 20nm, nó đòi hỏi sự hỗ trợ của máy ghi chùm tia điện tử đa tia (MBMW) hiện đại, và độ khó sản xuất, chi phí và áp lực về năng suất sẽ rất đáng kể đối với các kích thước chi tiết ngày càng lớn hơn.

Từ năm 2003, DNP đã tập trung vào việc phát triển các khuôn mẫu in nano (NIL), giúp giảm tiêu thụ năng lượng trong quá trình chiếu xạ bằng cách in trực tiếp và chuyển các khuôn mẫu có họa tiết mạch được khắc lên chất nền, và đã tích lũy được bí quyết kỹ thuật độc đáo.

DNP vừa công bố phát triển thành công khuôn mẫu in nano (NIL) có độ rộng đường kẻ 10nm, tương đương với quy trình 1,4nm hiện tại, có thể thay thế một số quy trình EUV và thậm chí cả quy trình EUV khẩu độ lớn (High NA) để sản xuất các chất bán dẫn logic tiên tiến, đáp ứng nhu cầu kiểm soát chi phí của khách hàng. Bằng việc cung cấp khuôn mẫu này, DNP sẽ mở rộng sự lựa chọn quy trình sản xuất chất bán dẫn cho khách hàng, từ đó giảm chi phí sản xuất và giảm thiểu tác động đến môi trường.

Theo các báo cáo, DNP sử dụng kỹ thuật tạo mẫu kép tự căn chỉnh (SADP) để thu nhỏ kích thước khuôn mẫu in nano với độ rộng đường kẻ là 10 nm. Công nghệ này tăng gấp đôi mật độ mẫu bằng cách lắng đọng và khắc các lớp màng mỏng trên các mẫu được tạo ra bởi hệ thống in thạch bản.

DNP chỉ ra rằng "quy trình tiết kiệm năng lượng bán dẫn siêu mịn sử dụng công nghệ in thạch bản nano" giúp giảm mức tiêu thụ điện năng xuống còn khoảng một phần mười so với các quy trình chiếu xạ truyền thống (như ArF/DUV ngâm, EUV).

Hiện tại, DNP đang liên hệ với các nhà sản xuất chất bán dẫn và các khách hàng khác, đồng thời đã bắt đầu đánh giá các khuôn mẫu in nano (NIL) với mục tiêu bắt đầu sản xuất hàng loạt vào năm 2027.

Nhìn về phía trước, để tiếp tục đạt được mục tiêu thu nhỏ bán dẫn và giảm chi phí, DNP tuyên bố sẽ tiếp tục thúc đẩy phát triển hơn nữa các khuôn mẫu NIL và tăng cường hệ thống sản xuất để đáp ứng nhu cầu ngày càng tăng, với mục tiêu tăng doanh thu NIL thêm 4 tỷ yên vào năm tài chính 2030.

Nguồn: Chip Intelligence