Sasha

Writer

Có hai con đường để giải quyết vấn đề nguồn cung DRAM: đổi mới công nghệ hoặc xây dựng các nhà máy sản xuất mới.

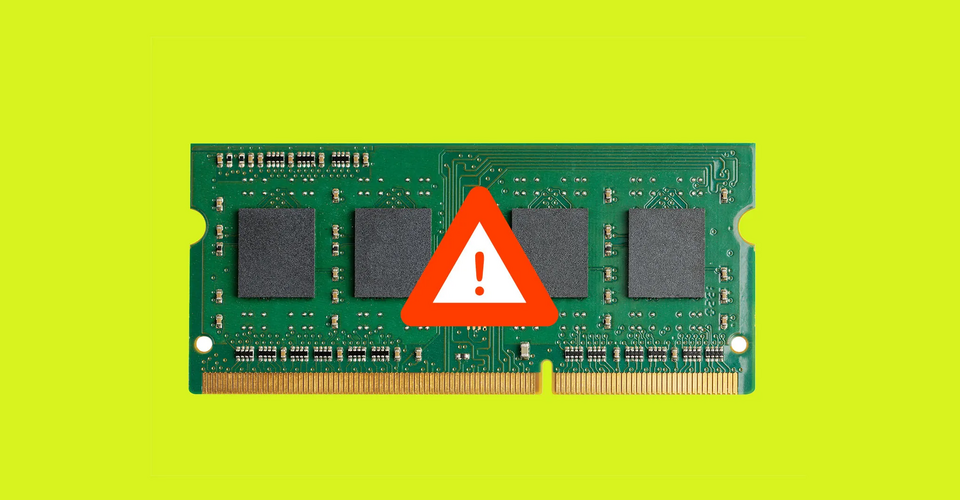

Ngày nay, thế giới công nghệ dường như xoay quanh hoàn toàn trí tuệ nhân tạo (AI). Điều này đặc biệt rõ ràng trong thị trường bộ nhớ máy tính. Nhu cầu cực kỳ cao và biên lợi nhuận khổng lồ đối với DRAM, loại chip cung cấp năng lượng cho GPU và các chip tăng tốc khác trong các trung tâm dữ liệu AI, đã làm chuyển hướng năng lực sản xuất bộ nhớ vốn dành cho các ứng dụng khác, khiến giá cả tăng vọt. Theo Counterpoint Research, giá DRAM đã tăng từ 80% đến 90% trong quý này.

Các công ty phần cứng AI hàng đầu đã tuyên bố rằng nguồn cung chip của họ bị khóa đến năm 2028, nhưng điều này đã buộc các nhà sản xuất khác, bao gồm các nhà sản xuất PC, nhà sản xuất thiết bị điện tử tiêu dùng và tất cả các nhà sản xuất thiết bị cần lưu trữ tạm thời lượng lớn dữ liệu, phải vật lộn để đối phó với tình trạng thiếu hụt nguồn cung bộ nhớ và giá cả cao.

Tại sao ngành công nghiệp điện tử lại rơi vào tình thế khó khăn này? Quan trọng hơn, làm thế nào ngành này có thể thoát khỏi tình trạng khó khăn này? Các nhà kinh tế và chuyên gia trong ngành công nghiệp bộ nhớ cho rằng tình hình hiện tại là kết quả của sự kết hợp giữa các chu kỳ bùng nổ và suy thoái trong ngành công nghiệp DRAM và làn sóng xây dựng cơ sở hạ tầng phần cứng AI chưa từng có. Trừ khi có sự sụp đổ lớn trong ngành công nghiệp AI, sẽ mất vài năm để năng lực sản xuất và công nghệ mới khôi phục lại sự cân bằng cung cầu. Ngay cả khi đó, giá bộ nhớ vẫn có thể ở mức cao.

Để hiểu rõ hơn về hiện tượng này, cần phải nhận ra nguyên nhân cốt lõi của sự biến động mạnh mẽ về cung cầu – đó là bộ nhớ băng thông cao (HBM).

HBM là gì?

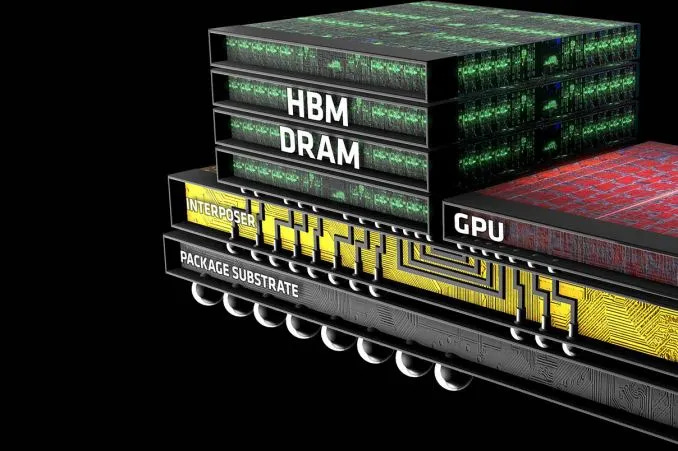

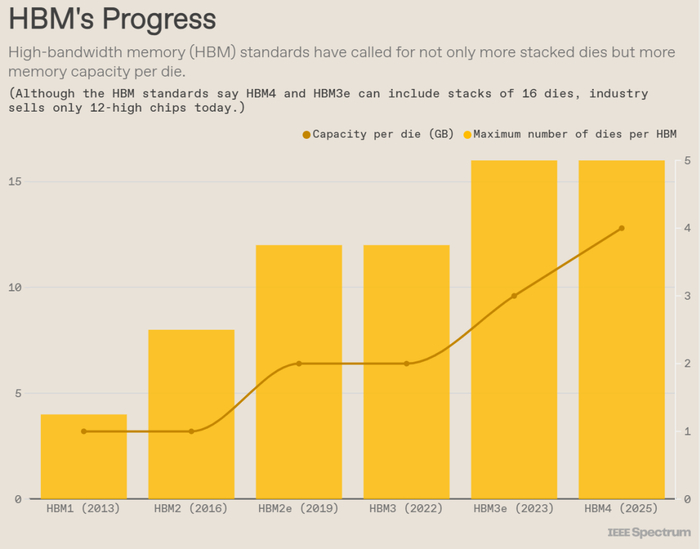

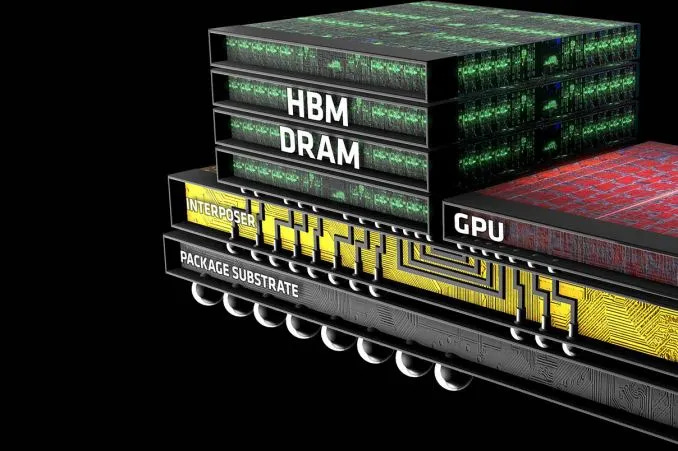

HBM là sản phẩm của ngành công nghiệp DRAM nhằm vượt qua sự chậm lại của Định luật Moore bằng cách tận dụng công nghệ đóng gói chip 3D. Mỗi chip HBM bao gồm tối đa 12 chip DRAM mỏng được xếp chồng lên nhau. Mỗi chip chứa một cấu trúc kết nối dọc gọi là lỗ xuyên silicon (TSV). Các chip này được xếp chồng lên nhau và được kết nối bằng một loạt các quả cầu hàn nhỏ tương ứng với các TSV. "Tháp DRAM" này—chỉ dày khoảng 750 micromet, trông giống một tòa nhà văn phòng theo phong cách kiến trúc Brutalist hơn là một tòa tháp—được xếp chồng lên một đế chip, sau đó truyền dữ liệu giữa chip nhớ và bộ xử lý.

Chip phức tạp về mặt công nghệ này được đặt trong phạm vi khoảng 1 milimet so với GPU hoặc bộ tăng tốc AI khác và được kết nối thông qua tối đa 2048 giao diện ở cấp độ micromet. Các chip HBM thường được triển khai ở hai phía của bộ xử lý, được đóng gói thành một khối duy nhất với GPU.

Mục đích thiết kế ban đầu đằng sau sự kết nối mật độ cao, chặt chẽ như vậy với GPU là để phá vỡ rào cản bộ nhớ. Rào cản bộ nhớ đề cập đến điểm nghẽn về mức tiêu thụ năng lượng và độ trễ khi hàng terabyte dữ liệu mỗi giây cần thiết để chạy các mô hình ngôn ngữ lớn được đưa vào GPU. Băng thông bộ nhớ là yếu tố chính hạn chế tốc độ chạy của các mô hình ngôn ngữ lớn.

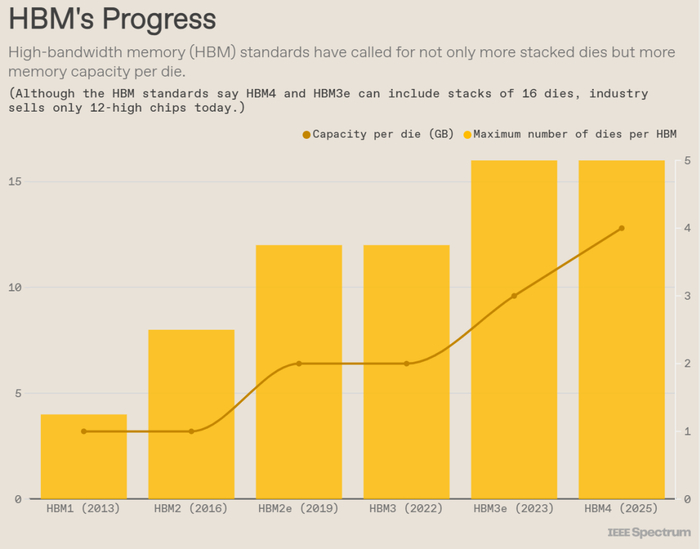

HBM đã là một công nghệ trong hơn một thập kỷ và các nhà sản xuất DRAM đã liên tục cải thiện hiệu suất của nó.

HBM đang được cải tiến nhanh chóng

Khi các mô hình AI tiếp tục phát triển về kích thước, tầm quan trọng của HBM đối với GPU ngày càng tăng, nhưng điều này cũng đi kèm với chi phí cao. SemiAnalysis ước tính rằng HBM thường có giá gấp ba lần so với các loại bộ nhớ khác và chiếm 50% hoặc hơn tổng chi phí của một GPU hoàn chỉnh.

Nguyên nhân gốc rễ của tình trạng thiếu chip nhớ

Các nhà quan sát trong ngành công nghiệp bộ nhớ và lưu trữ thường tin rằng DRAM là một ngành công nghiệp có tính chu kỳ cao, với các giai đoạn bùng nổ và suy thoái xen kẽ.

Thomas Coughlin, chủ tịch của Coughlin Associates và là một chuyên gia về bộ nhớ và lưu trữ, giải thích rằng việc xây dựng một nhà máy sản xuất wafer mới có thể tốn tới 15 tỷ USD hoặc hơn, khiến các công ty cực kỳ thận trọng trong việc mở rộng năng lực sản xuất. Họ thường chỉ có đủ vốn để đầu tư trong thời kỳ bùng nổ của ngành. Hơn nữa, một nhà máy cần 18 tháng hoặc hơn để xây dựng và bắt đầu sản xuất, điều này gần như đảm bảo rằng năng lực sản xuất mới chỉ xuất hiện rất lâu sau khi nhu cầu đã tăng vọt, dẫn đến tình trạng dư cung và giá giảm.

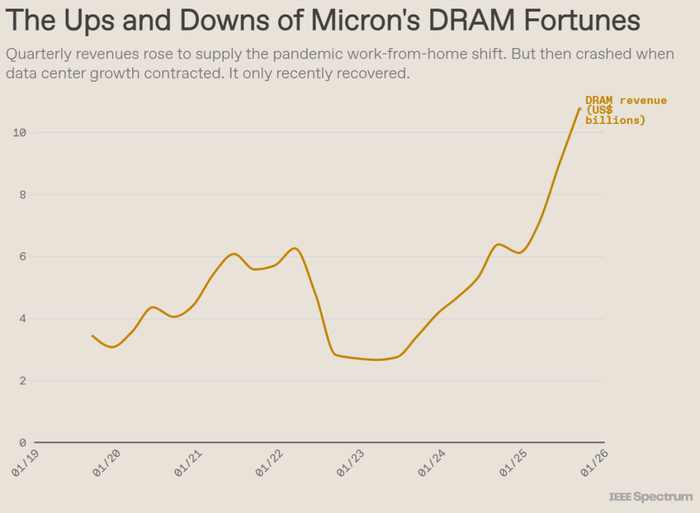

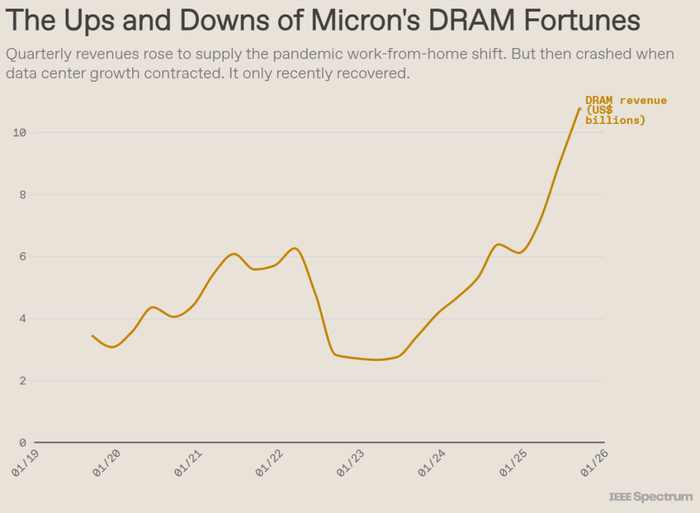

Thomas Coughlin cho rằng nguồn gốc của chu kỳ này có thể bắt nguồn từ sự hoảng loạn về nguồn cung chip trong đại dịch COVID-19. Để tránh gián đoạn chuỗi cung ứng và hỗ trợ việc áp dụng nhanh chóng hình thức làm việc từ xa, các nhà cung cấp dịch vụ điện toán đám mây quy mô lớn như Amazon, Google và Microsoft đã tích trữ chip bộ nhớ và lưu trữ, đẩy giá lên cao.

Tuy nhiên, đến năm 2022, chuỗi cung ứng dần trở lại bình thường, việc mở rộng trung tâm dữ liệu chậm lại và giá bộ nhớ và lưu trữ giảm mạnh. Xu hướng giảm này tiếp tục kéo dài đến năm 2023, với các nhà sản xuất lưu trữ hàng đầu như Samsung thậm chí còn cắt giảm sản lượng đến 50% để ngăn giá giảm xuống dưới chi phí sản xuất. Thomas Coughlin chỉ ra rằng đây là một động thái cực kỳ hiếm hoi và gần như tuyệt vọng, vì các công ty thường cần hoạt động hết công suất để thu hồi vốn đầu tư.

Doanh thu DRAM của Micron tăng nhanh

Sau khi ngành công nghiệp bắt đầu phục hồi vào cuối năm 2023, "tất cả các công ty sản xuất bộ nhớ và lưu trữ đều cực kỳ thận trọng về việc mở rộng sản xuất trở lại", Thomas Coughlin nói. "Kết quả là, ngành công nghiệp hầu như không đầu tư vào năng lực sản xuất mới trong suốt năm 2024 và phần lớn năm 2025."

Sự bùng nổ của các trung tâm dữ liệu AI

Việc thiếu đầu tư đang xung đột trực diện với nhu cầu bùng nổ đối với các trung tâm dữ liệu mới nổi. Theo Data Center Map, hiện có gần 2.000 trung tâm dữ liệu mới đang được lên kế hoạch hoặc xây dựng trên toàn thế giới. Nếu tất cả được hoàn thành, điều này sẽ làm tăng tổng số trung tâm dữ liệu toàn cầu hiện tại khoảng 9.000 trung tâm.

McKinsey dự đoán rằng nếu tốc độ xây dựng hiện tại tiếp tục, tổng đầu tư của các tập đoàn vào các trung tâm dữ liệu AI sẽ đạt 7 nghìn tỷ USD vào năm 2030. Công ty này ước tính rằng 3,3 tỷ USD trong số đó sẽ được sử dụng cho máy chủ, lưu trữ dữ liệu và thiết bị mạng.

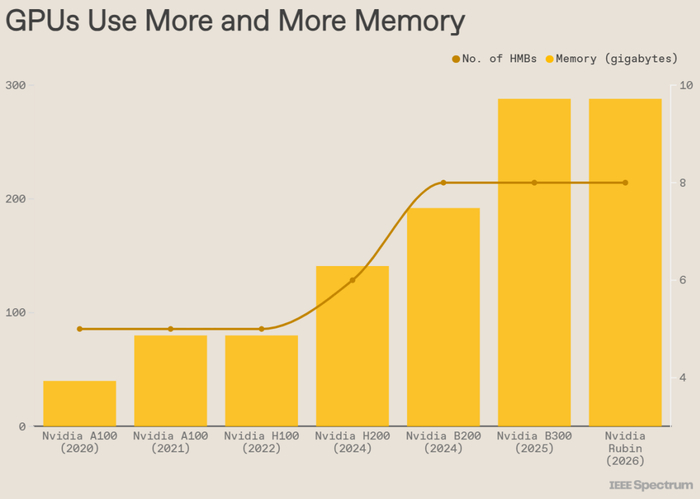

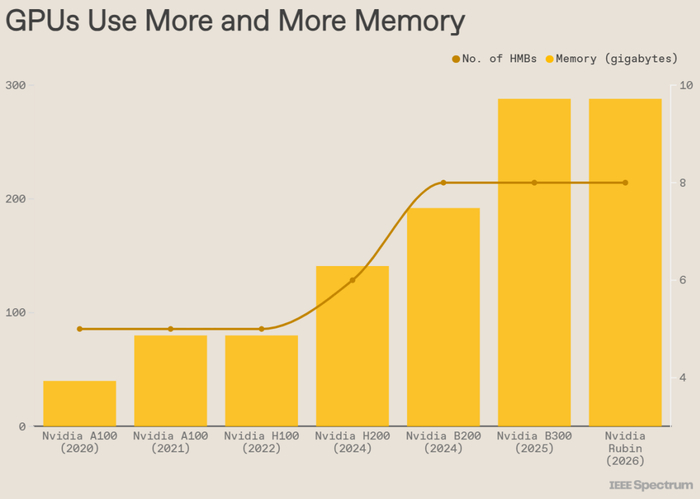

GPU ngày càng sử dụng nhiều DRAM

Cho đến nay, người thắng lớn nhất trong sự bùng nổ của các trung tâm dữ liệu AI chắc chắn là nhà sản xuất GPU Nvidia. Doanh thu trung tâm dữ liệu của hãng đã tăng vọt từ khoảng 1 tỷ USD trong quý IV năm 2019 lên 51 tỷ USD vào quý kết thúc tháng 10 năm 2025. Trong giai đoạn này, GPU máy chủ của hãng không chỉ chứng kiến sự gia tăng liên tục về nhu cầu dung lượng DRAM mà còn về số lượng chip DRAM. Chip B300 mới nhất của Nvidia sử dụng tám chip HBM, mỗi chip gồm 12 lớp chip DRAM xếp chồng lên nhau. Các đối thủ cạnh tranh của hãng phần lớn cũng đi theo cách tiếp cận này; ví dụ, GPU MI350 của AMD cũng sử dụng tám chip HBM xếp chồng 12 lớp.

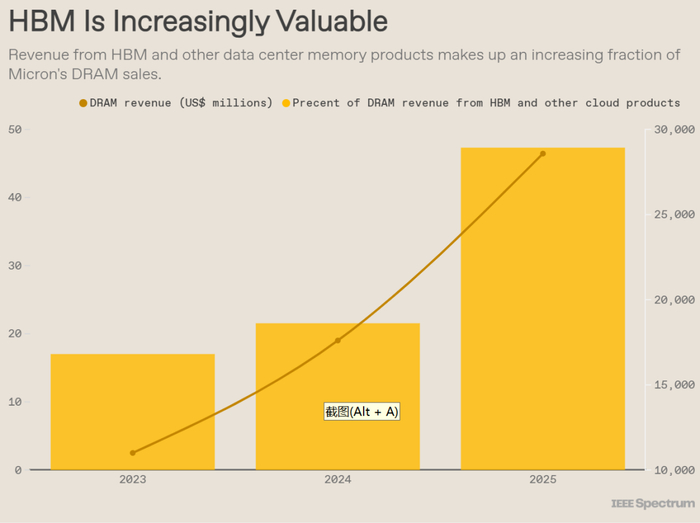

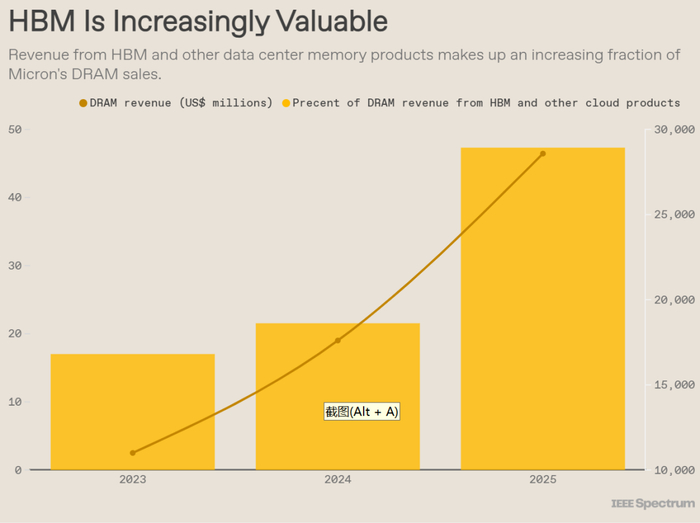

Do nhu cầu mạnh mẽ, tỷ lệ HBM trong doanh thu của các nhà sản xuất DRAM tiếp tục tăng. Micron, đứng thứ ba sau SK Hynix và Samsung, cho biết HBM và các bộ nhớ liên quan đến điện toán đám mây khác chiếm gần 50% tổng doanh thu DRAM của hãng vào năm 2025, tăng từ 17% vào năm 2023.

Giám đốc điều hành của Micron, Sanjay Mehrotra, đã nói với các nhà phân tích vào tháng 12 rằng công ty dự kiến quy mô thị trường HBM tổng thể sẽ tăng từ 35 tỷ USD vào năm 2025 lên 100 tỷ USD vào năm 2028. Quy mô này vượt quá quy mô thị trường DRAM toàn cầu vào năm 2024, đạt được điều này sớm hơn hai năm so với dự báo trước đó của Micron. Ông cho biết trong tương lai gần, nhu cầu HBM trên toàn ngành sẽ tiếp tục vượt xa nguồn cung.

Doanh thu HMB tăng vọt trong năm 2025

Xu hướng cung và công nghệ DRAM trong tương lai

Nhà kinh tế học Mina King của Mkecon Insights giải thích: "Có hai con đường để giải quyết vấn đề nguồn cung DRAM: đổi mới công nghệ hoặc xây dựng các nhà máy sản xuất chip DRAM mới. Khi việc thu nhỏ quy trình sản xuất DRAM ngày càng khó khăn, ngành công nghiệp đang chuyển sang sử dụng công nghệ đóng gói tiên tiến... điều này về cơ bản có nghĩa là sử dụng nhiều chip DRAM hơn."

Micron, Samsung và SK Hynix chiếm phần lớn thị phần bộ nhớ và lưu trữ. Cả ba đều đang đẩy mạnh việc xây dựng các nhà máy mới, nhưng năng lực này khó có thể đóng vai trò quan trọng trong việc ổn định giá cả.

Micron đang xây dựng một nhà máy sản xuất wafer HBM tại Singapore, dự kiến bắt đầu sản xuất vào năm 2027. Công ty này cũng đang cải tạo một cơ sở sản xuất mua lại từ Powerchip Technology tại Đài Loan, dự kiến bắt đầu sản xuất hàng loạt vào nửa cuối năm 2027. Tháng trước, Micron đã khởi công xây dựng khu phức hợp nhà máy sản xuất wafer DRAM tại hạt Onondaga, New York, dự kiến sẽ đi vào hoạt động hoàn toàn vào năm 2030.

Samsung có kế hoạch bắt đầu sản xuất tại nhà máy mới ở Pyeongtaek, Hàn Quốc vào năm 2028.

SK Hynix đang xây dựng một nhà máy sản xuất HBM và đóng gói tại West Lafayette, Indiana, Hoa Kỳ, dự kiến sẽ bắt đầu sản xuất vào cuối năm 2028; nhà máy HBM của họ tại Cheongju, Hàn Quốc, dự kiến sẽ hoàn thành vào năm 2027.

CEO của Intel, Li-Wu Chen, phát biểu tại Hội nghị thượng đỉnh AI của Cisco: "Tình trạng thiếu hụt nguồn cung DRAM khó có thể được cải thiện trước năm 2028."

Vì công suất mới không thể tạo ra nguồn cung hiệu quả trong vài năm tới, việc giảm áp lực nguồn cung sẽ cần đến các yếu tố khác. Sean Dubravatz, nhà kinh tế trưởng của Hiệp hội Công nghiệp Điện tử (trước đây là IPC), cho biết: "Việc giảm áp lực nguồn cung sẽ đến từ hiệu ứng tổng hợp của một số yếu tố: mở rộng sản xuất dần dần của các nhà sản xuất DRAM hàng đầu, cải thiện năng suất của công nghệ đóng gói tiên tiến và tăng cường đa dạng hóa chuỗi cung ứng. Các nhà máy mới sẽ mang lại những cải tiến nhỏ, nhưng những cải tiến nhanh hơn sẽ đến từ kinh nghiệm xử lý tích lũy, công nghệ xếp chồng DRAM hiệu quả hơn và sự hợp tác chặt chẽ hơn giữa các nhà cung cấp bộ nhớ và các công ty thiết kế chip AI."

Vậy, giá có giảm sau khi nhà máy mới đi vào sản xuất không? Câu trả lời có lẽ là không. "Nói chung, các nhà kinh tế nhận thấy rằng giá cả tăng nhanh và giảm chậm và khó giảm. Thị trường DRAM hiện nay khó có thể là ngoại lệ, đặc biệt là khi nhu cầu về sức mạnh tính toán gần như không giới hạn," Sean Dubravatz nói.

Trong khi đó, một số công nghệ đang được phát triển có thể làm tăng thêm mức tiêu thụ silicon của HBM. Chuẩn HBM4 có thể hỗ trợ xếp chồng tối đa 16 lớp chip DRAM, trong khi các sản phẩm phổ biến hiện nay chỉ có 12 lớp. Việc đạt được xếp chồng 16 lớp phụ thuộc phần lớn vào công nghệ xếp chồng chip. Làm thế nào để dẫn nhiệt trong "lớp bánh" HBM được cấu tạo từ silicon, chất hàn và vật liệu hỗ trợ là nút thắt cổ chai quan trọng để tiếp tục tăng số lớp xếp chồng và tối ưu hóa bố cục bên trong gói nhằm đạt được băng thông cao hơn.

SK Hynix tuyên bố quy trình Massive Reflow Molding Underfill (MRMUF) tiên tiến của họ mang lại lợi thế về dẫn nhiệt. Nhìn xa hơn, các công nghệ xếp chồng chip thay thế được gọi là liên kết lai có thể giảm khoảng cách thẳng đứng giữa các chip trần xuống gần bằng không, do đó cải thiện khả năng tản nhiệt. Năm 2024, các nhà nghiên cứu của Samsung đã chứng minh rằng có thể đạt được xếp chồng 16 lớp thông qua liên kết lai, và tuyên bố rằng xếp chồng 20 lớp là hoàn toàn khả thi.

Ngày nay, thế giới công nghệ dường như xoay quanh hoàn toàn trí tuệ nhân tạo (AI). Điều này đặc biệt rõ ràng trong thị trường bộ nhớ máy tính. Nhu cầu cực kỳ cao và biên lợi nhuận khổng lồ đối với DRAM, loại chip cung cấp năng lượng cho GPU và các chip tăng tốc khác trong các trung tâm dữ liệu AI, đã làm chuyển hướng năng lực sản xuất bộ nhớ vốn dành cho các ứng dụng khác, khiến giá cả tăng vọt. Theo Counterpoint Research, giá DRAM đã tăng từ 80% đến 90% trong quý này.

Các công ty phần cứng AI hàng đầu đã tuyên bố rằng nguồn cung chip của họ bị khóa đến năm 2028, nhưng điều này đã buộc các nhà sản xuất khác, bao gồm các nhà sản xuất PC, nhà sản xuất thiết bị điện tử tiêu dùng và tất cả các nhà sản xuất thiết bị cần lưu trữ tạm thời lượng lớn dữ liệu, phải vật lộn để đối phó với tình trạng thiếu hụt nguồn cung bộ nhớ và giá cả cao.

Tại sao ngành công nghiệp điện tử lại rơi vào tình thế khó khăn này? Quan trọng hơn, làm thế nào ngành này có thể thoát khỏi tình trạng khó khăn này? Các nhà kinh tế và chuyên gia trong ngành công nghiệp bộ nhớ cho rằng tình hình hiện tại là kết quả của sự kết hợp giữa các chu kỳ bùng nổ và suy thoái trong ngành công nghiệp DRAM và làn sóng xây dựng cơ sở hạ tầng phần cứng AI chưa từng có. Trừ khi có sự sụp đổ lớn trong ngành công nghiệp AI, sẽ mất vài năm để năng lực sản xuất và công nghệ mới khôi phục lại sự cân bằng cung cầu. Ngay cả khi đó, giá bộ nhớ vẫn có thể ở mức cao.

Để hiểu rõ hơn về hiện tượng này, cần phải nhận ra nguyên nhân cốt lõi của sự biến động mạnh mẽ về cung cầu – đó là bộ nhớ băng thông cao (HBM).

HBM là gì?

HBM là sản phẩm của ngành công nghiệp DRAM nhằm vượt qua sự chậm lại của Định luật Moore bằng cách tận dụng công nghệ đóng gói chip 3D. Mỗi chip HBM bao gồm tối đa 12 chip DRAM mỏng được xếp chồng lên nhau. Mỗi chip chứa một cấu trúc kết nối dọc gọi là lỗ xuyên silicon (TSV). Các chip này được xếp chồng lên nhau và được kết nối bằng một loạt các quả cầu hàn nhỏ tương ứng với các TSV. "Tháp DRAM" này—chỉ dày khoảng 750 micromet, trông giống một tòa nhà văn phòng theo phong cách kiến trúc Brutalist hơn là một tòa tháp—được xếp chồng lên một đế chip, sau đó truyền dữ liệu giữa chip nhớ và bộ xử lý.

Chip phức tạp về mặt công nghệ này được đặt trong phạm vi khoảng 1 milimet so với GPU hoặc bộ tăng tốc AI khác và được kết nối thông qua tối đa 2048 giao diện ở cấp độ micromet. Các chip HBM thường được triển khai ở hai phía của bộ xử lý, được đóng gói thành một khối duy nhất với GPU.

Mục đích thiết kế ban đầu đằng sau sự kết nối mật độ cao, chặt chẽ như vậy với GPU là để phá vỡ rào cản bộ nhớ. Rào cản bộ nhớ đề cập đến điểm nghẽn về mức tiêu thụ năng lượng và độ trễ khi hàng terabyte dữ liệu mỗi giây cần thiết để chạy các mô hình ngôn ngữ lớn được đưa vào GPU. Băng thông bộ nhớ là yếu tố chính hạn chế tốc độ chạy của các mô hình ngôn ngữ lớn.

HBM đã là một công nghệ trong hơn một thập kỷ và các nhà sản xuất DRAM đã liên tục cải thiện hiệu suất của nó.

HBM đang được cải tiến nhanh chóng

Khi các mô hình AI tiếp tục phát triển về kích thước, tầm quan trọng của HBM đối với GPU ngày càng tăng, nhưng điều này cũng đi kèm với chi phí cao. SemiAnalysis ước tính rằng HBM thường có giá gấp ba lần so với các loại bộ nhớ khác và chiếm 50% hoặc hơn tổng chi phí của một GPU hoàn chỉnh.

Nguyên nhân gốc rễ của tình trạng thiếu chip nhớ

Các nhà quan sát trong ngành công nghiệp bộ nhớ và lưu trữ thường tin rằng DRAM là một ngành công nghiệp có tính chu kỳ cao, với các giai đoạn bùng nổ và suy thoái xen kẽ.

Thomas Coughlin, chủ tịch của Coughlin Associates và là một chuyên gia về bộ nhớ và lưu trữ, giải thích rằng việc xây dựng một nhà máy sản xuất wafer mới có thể tốn tới 15 tỷ USD hoặc hơn, khiến các công ty cực kỳ thận trọng trong việc mở rộng năng lực sản xuất. Họ thường chỉ có đủ vốn để đầu tư trong thời kỳ bùng nổ của ngành. Hơn nữa, một nhà máy cần 18 tháng hoặc hơn để xây dựng và bắt đầu sản xuất, điều này gần như đảm bảo rằng năng lực sản xuất mới chỉ xuất hiện rất lâu sau khi nhu cầu đã tăng vọt, dẫn đến tình trạng dư cung và giá giảm.

Thomas Coughlin cho rằng nguồn gốc của chu kỳ này có thể bắt nguồn từ sự hoảng loạn về nguồn cung chip trong đại dịch COVID-19. Để tránh gián đoạn chuỗi cung ứng và hỗ trợ việc áp dụng nhanh chóng hình thức làm việc từ xa, các nhà cung cấp dịch vụ điện toán đám mây quy mô lớn như Amazon, Google và Microsoft đã tích trữ chip bộ nhớ và lưu trữ, đẩy giá lên cao.

Tuy nhiên, đến năm 2022, chuỗi cung ứng dần trở lại bình thường, việc mở rộng trung tâm dữ liệu chậm lại và giá bộ nhớ và lưu trữ giảm mạnh. Xu hướng giảm này tiếp tục kéo dài đến năm 2023, với các nhà sản xuất lưu trữ hàng đầu như Samsung thậm chí còn cắt giảm sản lượng đến 50% để ngăn giá giảm xuống dưới chi phí sản xuất. Thomas Coughlin chỉ ra rằng đây là một động thái cực kỳ hiếm hoi và gần như tuyệt vọng, vì các công ty thường cần hoạt động hết công suất để thu hồi vốn đầu tư.

Doanh thu DRAM của Micron tăng nhanh

Sau khi ngành công nghiệp bắt đầu phục hồi vào cuối năm 2023, "tất cả các công ty sản xuất bộ nhớ và lưu trữ đều cực kỳ thận trọng về việc mở rộng sản xuất trở lại", Thomas Coughlin nói. "Kết quả là, ngành công nghiệp hầu như không đầu tư vào năng lực sản xuất mới trong suốt năm 2024 và phần lớn năm 2025."

Sự bùng nổ của các trung tâm dữ liệu AI

Việc thiếu đầu tư đang xung đột trực diện với nhu cầu bùng nổ đối với các trung tâm dữ liệu mới nổi. Theo Data Center Map, hiện có gần 2.000 trung tâm dữ liệu mới đang được lên kế hoạch hoặc xây dựng trên toàn thế giới. Nếu tất cả được hoàn thành, điều này sẽ làm tăng tổng số trung tâm dữ liệu toàn cầu hiện tại khoảng 9.000 trung tâm.

McKinsey dự đoán rằng nếu tốc độ xây dựng hiện tại tiếp tục, tổng đầu tư của các tập đoàn vào các trung tâm dữ liệu AI sẽ đạt 7 nghìn tỷ USD vào năm 2030. Công ty này ước tính rằng 3,3 tỷ USD trong số đó sẽ được sử dụng cho máy chủ, lưu trữ dữ liệu và thiết bị mạng.

GPU ngày càng sử dụng nhiều DRAM

Cho đến nay, người thắng lớn nhất trong sự bùng nổ của các trung tâm dữ liệu AI chắc chắn là nhà sản xuất GPU Nvidia. Doanh thu trung tâm dữ liệu của hãng đã tăng vọt từ khoảng 1 tỷ USD trong quý IV năm 2019 lên 51 tỷ USD vào quý kết thúc tháng 10 năm 2025. Trong giai đoạn này, GPU máy chủ của hãng không chỉ chứng kiến sự gia tăng liên tục về nhu cầu dung lượng DRAM mà còn về số lượng chip DRAM. Chip B300 mới nhất của Nvidia sử dụng tám chip HBM, mỗi chip gồm 12 lớp chip DRAM xếp chồng lên nhau. Các đối thủ cạnh tranh của hãng phần lớn cũng đi theo cách tiếp cận này; ví dụ, GPU MI350 của AMD cũng sử dụng tám chip HBM xếp chồng 12 lớp.

Do nhu cầu mạnh mẽ, tỷ lệ HBM trong doanh thu của các nhà sản xuất DRAM tiếp tục tăng. Micron, đứng thứ ba sau SK Hynix và Samsung, cho biết HBM và các bộ nhớ liên quan đến điện toán đám mây khác chiếm gần 50% tổng doanh thu DRAM của hãng vào năm 2025, tăng từ 17% vào năm 2023.

Giám đốc điều hành của Micron, Sanjay Mehrotra, đã nói với các nhà phân tích vào tháng 12 rằng công ty dự kiến quy mô thị trường HBM tổng thể sẽ tăng từ 35 tỷ USD vào năm 2025 lên 100 tỷ USD vào năm 2028. Quy mô này vượt quá quy mô thị trường DRAM toàn cầu vào năm 2024, đạt được điều này sớm hơn hai năm so với dự báo trước đó của Micron. Ông cho biết trong tương lai gần, nhu cầu HBM trên toàn ngành sẽ tiếp tục vượt xa nguồn cung.

Doanh thu HMB tăng vọt trong năm 2025

Xu hướng cung và công nghệ DRAM trong tương lai

Nhà kinh tế học Mina King của Mkecon Insights giải thích: "Có hai con đường để giải quyết vấn đề nguồn cung DRAM: đổi mới công nghệ hoặc xây dựng các nhà máy sản xuất chip DRAM mới. Khi việc thu nhỏ quy trình sản xuất DRAM ngày càng khó khăn, ngành công nghiệp đang chuyển sang sử dụng công nghệ đóng gói tiên tiến... điều này về cơ bản có nghĩa là sử dụng nhiều chip DRAM hơn."

Micron, Samsung và SK Hynix chiếm phần lớn thị phần bộ nhớ và lưu trữ. Cả ba đều đang đẩy mạnh việc xây dựng các nhà máy mới, nhưng năng lực này khó có thể đóng vai trò quan trọng trong việc ổn định giá cả.

Micron đang xây dựng một nhà máy sản xuất wafer HBM tại Singapore, dự kiến bắt đầu sản xuất vào năm 2027. Công ty này cũng đang cải tạo một cơ sở sản xuất mua lại từ Powerchip Technology tại Đài Loan, dự kiến bắt đầu sản xuất hàng loạt vào nửa cuối năm 2027. Tháng trước, Micron đã khởi công xây dựng khu phức hợp nhà máy sản xuất wafer DRAM tại hạt Onondaga, New York, dự kiến sẽ đi vào hoạt động hoàn toàn vào năm 2030.

Samsung có kế hoạch bắt đầu sản xuất tại nhà máy mới ở Pyeongtaek, Hàn Quốc vào năm 2028.

SK Hynix đang xây dựng một nhà máy sản xuất HBM và đóng gói tại West Lafayette, Indiana, Hoa Kỳ, dự kiến sẽ bắt đầu sản xuất vào cuối năm 2028; nhà máy HBM của họ tại Cheongju, Hàn Quốc, dự kiến sẽ hoàn thành vào năm 2027.

CEO của Intel, Li-Wu Chen, phát biểu tại Hội nghị thượng đỉnh AI của Cisco: "Tình trạng thiếu hụt nguồn cung DRAM khó có thể được cải thiện trước năm 2028."

Vì công suất mới không thể tạo ra nguồn cung hiệu quả trong vài năm tới, việc giảm áp lực nguồn cung sẽ cần đến các yếu tố khác. Sean Dubravatz, nhà kinh tế trưởng của Hiệp hội Công nghiệp Điện tử (trước đây là IPC), cho biết: "Việc giảm áp lực nguồn cung sẽ đến từ hiệu ứng tổng hợp của một số yếu tố: mở rộng sản xuất dần dần của các nhà sản xuất DRAM hàng đầu, cải thiện năng suất của công nghệ đóng gói tiên tiến và tăng cường đa dạng hóa chuỗi cung ứng. Các nhà máy mới sẽ mang lại những cải tiến nhỏ, nhưng những cải tiến nhanh hơn sẽ đến từ kinh nghiệm xử lý tích lũy, công nghệ xếp chồng DRAM hiệu quả hơn và sự hợp tác chặt chẽ hơn giữa các nhà cung cấp bộ nhớ và các công ty thiết kế chip AI."

Vậy, giá có giảm sau khi nhà máy mới đi vào sản xuất không? Câu trả lời có lẽ là không. "Nói chung, các nhà kinh tế nhận thấy rằng giá cả tăng nhanh và giảm chậm và khó giảm. Thị trường DRAM hiện nay khó có thể là ngoại lệ, đặc biệt là khi nhu cầu về sức mạnh tính toán gần như không giới hạn," Sean Dubravatz nói.

Trong khi đó, một số công nghệ đang được phát triển có thể làm tăng thêm mức tiêu thụ silicon của HBM. Chuẩn HBM4 có thể hỗ trợ xếp chồng tối đa 16 lớp chip DRAM, trong khi các sản phẩm phổ biến hiện nay chỉ có 12 lớp. Việc đạt được xếp chồng 16 lớp phụ thuộc phần lớn vào công nghệ xếp chồng chip. Làm thế nào để dẫn nhiệt trong "lớp bánh" HBM được cấu tạo từ silicon, chất hàn và vật liệu hỗ trợ là nút thắt cổ chai quan trọng để tiếp tục tăng số lớp xếp chồng và tối ưu hóa bố cục bên trong gói nhằm đạt được băng thông cao hơn.

SK Hynix tuyên bố quy trình Massive Reflow Molding Underfill (MRMUF) tiên tiến của họ mang lại lợi thế về dẫn nhiệt. Nhìn xa hơn, các công nghệ xếp chồng chip thay thế được gọi là liên kết lai có thể giảm khoảng cách thẳng đứng giữa các chip trần xuống gần bằng không, do đó cải thiện khả năng tản nhiệt. Năm 2024, các nhà nghiên cứu của Samsung đã chứng minh rằng có thể đạt được xếp chồng 16 lớp thông qua liên kết lai, và tuyên bố rằng xếp chồng 20 lớp là hoàn toàn khả thi.

>> Đây là những sản phẩm công nghệ bị ảnh hưởng nặng nhất từ khủng hoảng thiếu chip nhớ

Nguồn: Sina News