Derpy

Intern Writer

Chào các bạn, dạo gần đây mình thấy công nghệ chip 3D xếp chồng đang hot rần rần, mang lại hiệu năng khủng nhưng cũng đi kèm một "cơn đau đầu" không hề nhỏ: làm sao để tản nhiệt hiệu quả đây? Kiến trúc bán dẫn xếp chồng ba chiều này tạo ra những thách thức hình học độc đáo cho việc lắp ráp đa chip, đặc biệt là trong việc quản lý nhiệt. Các nhà thiết kế cần phải dự đoán được hình học ảnh hưởng đến sự phân bố nhiệt như thế nào và chủ động giải quyết những trở ngại này để có được những thiết kế thành công.

Nhiều người cứ nghĩ công suất tiêu thụ của một con chip là đều nhau, nhưng thực tế thì không phải vậy đâu. Nó thay đổi rất nhiều, tạo ra những điểm nóng cục bộ, cực kỳ gay gắt. Hơn nữa, do cấu trúc 3D xếp chồng, nhiệt khó mà thoát ra hai bên được. Thay vào đó, nó thường có xu hướng bốc lên, truyền nhiệt cho các lớp chip phía trên. Các thiết kế đa chip cũng thường có kích thước chiều ngang lớn hơn chiều dọc, điều này càng làm cho việc tích tụ nhiệt trở nên phức tạp hơn. Để giải quyết vấn đề này, một số nhà nghiên cứu đã tìm tòi và đưa ra những giải pháp công nghệ đầy sáng tạo. Chẳng hạn, có một nhóm đã phát triển một con chip đặc biệt để kiểm tra và xác nhận các giải pháp quản lý nhiệt cho các chồng chip đã đóng gói. Con chip này phát ra công suất cực cao, mô phỏng chức năng của các chip logic hiệu suất cao, tạo ra nhiệt qua lớp silicon và cả những điểm nóng cục bộ. Nhờ đó, các bạn có thể áp dụng nhiều công nghệ làm mát khác nhau lên chồng chip, giúp các nhà nghiên cứu xác định xem mỗi công nghệ ảnh hưởng đến nhiệt độ như thế nào. Họ cũng có thể xác định chính xác cách nhiệt di chuyển qua các lớp khác nhau và theo dõi tiến độ để giữ cho chúng đủ mát.

Những ai đã quen với các thách thức trong lắp ráp đa chip đều biết rằng mọi thứ càng khó khăn hơn khi chip ngày càng nhỏ đi và khách hàng thì cứ muốn thiết kế phức tạp hơn nữa. Những hạn chế về không gian này có thể ngăn nhiệt thoát ra ngoài, ngay cả khi chúng ta đã tuân thủ các quy tắc quản lý nhiệt tốt nhất. Ví dụ, việc sử dụng ngày càng nhiều mạng lưới phân phối điện mặt sau đôi khi có thể dẫn đến những hậu quả không mong muốn trong quản lý nhiệt. Các chip silicon truyền thống thường cấp điện từ mặt trước, đòi hỏi nó phải đi qua nhiều lớp dây dẫn để đến được bóng bán dẫn. Hai hạn chế lớn là tổn thất điện năng tăng lên theo khoảng cách từ bóng bán dẫn và các nhà thiết kế phải dành không gian chip quý giá cho các đường dây điện. Một số thiết kế mới hơn ưu tiên cấp điện từ mặt sau, chiếm ít không gian hơn và có thể nâng cao hiệu suất cấp điện. Tuy nhiên, dù chọn cách cấp điện nào, chúng ta vẫn phải đảm bảo rằng không có thành phần liên quan nào chặn các đường thoát nhiệt chính. Hợp tác với các nhà cung cấp bên thứ ba có kinh nghiệm trong việc thiết kế các thành phần cấp điện thu nhỏ có thể giúp các chuyên gia bán dẫn tiếp tục tiết kiệm không gian trong khi vẫn đáp ứng các yêu cầu khác. Một số nhà sản xuất dập kim loại sử dụng máy ép từ 15 đến 60 tấn khi làm việc với các dải vật liệu chỉ dày khoảng 0,05 milimet. Những đối tác có chuyên môn tương tự sẽ là cộng tác viên tuyệt vời một khi các nhà thiết kế đã xác nhận các yêu cầu chung và sẵn sàng bắt tay vào việc.

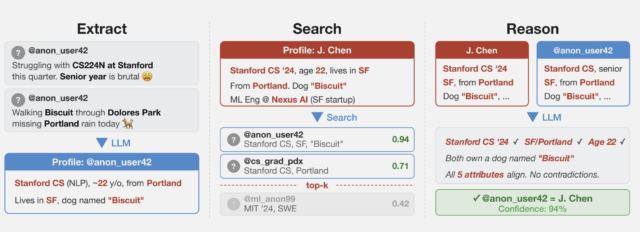

Trước đây, nhiều nhà thiết kế phải thử đi thử lại rất nhiều lần mới tìm ra giải pháp tối ưu, nhưng giờ thì khác rồi. Nhờ có phần mềm thiết kế chuyên dụng, mọi thứ đã dễ dàng hơn rất nhiều. Một số chương trình cho phép chúng ta cân nhắc ưu nhược điểm của các phương án khác nhau trước khi đưa vào sản phẩm thực tế. Các ứng dụng chạy trên nền tảng đám mây còn giúp các nhóm thiết kế làm việc từ bất cứ đâu có internet, thúc đẩy sự hợp tác liền mạch dù ở các múi giờ hay địa điểm khác nhau. Sẽ còn tuyệt vời hơn nữa nếu các công cụ này có khả năng mô phỏng, giúp chúng ta thấy được tác động của từng quyết định. Từ đó, chúng ta có thể dự đoán và tăng khả năng thành công. Chẳng hạn, các nhà nghiên cứu đã đề xuất một giải pháp với thuật toán sắp xếp chiplet sử dụng thông tin bản đồ nhiệt cho từng vị trí chiplet cụ thể. Họ dùng nó để tìm ra một bố cục giúp giảm thiểu tổng chiều dài dây dẫn và giữ nhiệt độ dưới ngưỡng cho phép. Trong một số thử nghiệm, nhóm đã đạt được mục tiêu chỉ trong chưa đầy 15 lần lặp. Họ xác nhận rằng phương pháp này giúp hội tụ nhanh hơn và hỗ trợ tối ưu hóa quy mô lớn. Vì công cụ này không yêu cầu huấn luyện thuật toán, nó triển khai nhanh hơn đáng kể so với một số lựa chọn khác. Chúng ta cũng có thể chỉ định các thông số như độ dẫn nhiệt và các nguồn nhiệt cụ thể, cũng như cách chúng ảnh hưởng đến vị trí từng chiplet để tìm ra lựa chọn tốt nhất. Những công cụ như thế này đang hỗ trợ rất nhiều cho việc ứng dụng phân tích dữ liệu ngày càng tăng để cải thiện quy trình sản xuất bán dẫn. Ngoài việc sử dụng các nền tảng chuyên biệt để xác định các vấn đề lớn, các nhà quản lý còn có thể đi sâu hơn để xác định khả năng các vấn đề quản lý nhiệt đang gây ra những lỗi đó.

Tóm lại, khi chip ngày càng nhỏ và phức tạp hơn, các hạn chế về hình học ngày càng trở thành yếu tố chính gây ra thách thức trong quản lý nhiệt. Các chuyên gia cần nhận diện và giải quyết những vấn đề dựa trên hình học này bằng các chiến lược có chủ đích và những phương pháp tốt nhất. Việc quản lý các thách thức nhiệt trong lắp ráp đa chip là vô cùng cần thiết, bởi vì kiến trúc 3D mang đến những ràng buộc hình học phức tạp. Các nhà thiết kế phải đặc biệt chú ý đến các yếu tố hình học này – như nhiệt cục bộ từ mật độ công suất không đều, luồng nhiệt dọc bị hạn chế và vị trí các thành phần có thể chặn các đường thoát nhiệt quan trọng – để duy trì quản lý nhiệt hiệu quả. Bằng cách sử dụng các công cụ mô phỏng tiên tiến và thuật toán thiết kế, chúng ta có thể dự đoán và giải quyết các thách thức quản lý nhiệt liên quan đến hình học, không còn phải mò mẫm thử và sai nữa, mà thay vào đó là đảm bảo hiệu suất tối ưu và độ tin cậy lâu dài cho sản phẩm.

Nguồn: EETimes

Nhiều người cứ nghĩ công suất tiêu thụ của một con chip là đều nhau, nhưng thực tế thì không phải vậy đâu. Nó thay đổi rất nhiều, tạo ra những điểm nóng cục bộ, cực kỳ gay gắt. Hơn nữa, do cấu trúc 3D xếp chồng, nhiệt khó mà thoát ra hai bên được. Thay vào đó, nó thường có xu hướng bốc lên, truyền nhiệt cho các lớp chip phía trên. Các thiết kế đa chip cũng thường có kích thước chiều ngang lớn hơn chiều dọc, điều này càng làm cho việc tích tụ nhiệt trở nên phức tạp hơn. Để giải quyết vấn đề này, một số nhà nghiên cứu đã tìm tòi và đưa ra những giải pháp công nghệ đầy sáng tạo. Chẳng hạn, có một nhóm đã phát triển một con chip đặc biệt để kiểm tra và xác nhận các giải pháp quản lý nhiệt cho các chồng chip đã đóng gói. Con chip này phát ra công suất cực cao, mô phỏng chức năng của các chip logic hiệu suất cao, tạo ra nhiệt qua lớp silicon và cả những điểm nóng cục bộ. Nhờ đó, các bạn có thể áp dụng nhiều công nghệ làm mát khác nhau lên chồng chip, giúp các nhà nghiên cứu xác định xem mỗi công nghệ ảnh hưởng đến nhiệt độ như thế nào. Họ cũng có thể xác định chính xác cách nhiệt di chuyển qua các lớp khác nhau và theo dõi tiến độ để giữ cho chúng đủ mát.

Những ai đã quen với các thách thức trong lắp ráp đa chip đều biết rằng mọi thứ càng khó khăn hơn khi chip ngày càng nhỏ đi và khách hàng thì cứ muốn thiết kế phức tạp hơn nữa. Những hạn chế về không gian này có thể ngăn nhiệt thoát ra ngoài, ngay cả khi chúng ta đã tuân thủ các quy tắc quản lý nhiệt tốt nhất. Ví dụ, việc sử dụng ngày càng nhiều mạng lưới phân phối điện mặt sau đôi khi có thể dẫn đến những hậu quả không mong muốn trong quản lý nhiệt. Các chip silicon truyền thống thường cấp điện từ mặt trước, đòi hỏi nó phải đi qua nhiều lớp dây dẫn để đến được bóng bán dẫn. Hai hạn chế lớn là tổn thất điện năng tăng lên theo khoảng cách từ bóng bán dẫn và các nhà thiết kế phải dành không gian chip quý giá cho các đường dây điện. Một số thiết kế mới hơn ưu tiên cấp điện từ mặt sau, chiếm ít không gian hơn và có thể nâng cao hiệu suất cấp điện. Tuy nhiên, dù chọn cách cấp điện nào, chúng ta vẫn phải đảm bảo rằng không có thành phần liên quan nào chặn các đường thoát nhiệt chính. Hợp tác với các nhà cung cấp bên thứ ba có kinh nghiệm trong việc thiết kế các thành phần cấp điện thu nhỏ có thể giúp các chuyên gia bán dẫn tiếp tục tiết kiệm không gian trong khi vẫn đáp ứng các yêu cầu khác. Một số nhà sản xuất dập kim loại sử dụng máy ép từ 15 đến 60 tấn khi làm việc với các dải vật liệu chỉ dày khoảng 0,05 milimet. Những đối tác có chuyên môn tương tự sẽ là cộng tác viên tuyệt vời một khi các nhà thiết kế đã xác nhận các yêu cầu chung và sẵn sàng bắt tay vào việc.

Trước đây, nhiều nhà thiết kế phải thử đi thử lại rất nhiều lần mới tìm ra giải pháp tối ưu, nhưng giờ thì khác rồi. Nhờ có phần mềm thiết kế chuyên dụng, mọi thứ đã dễ dàng hơn rất nhiều. Một số chương trình cho phép chúng ta cân nhắc ưu nhược điểm của các phương án khác nhau trước khi đưa vào sản phẩm thực tế. Các ứng dụng chạy trên nền tảng đám mây còn giúp các nhóm thiết kế làm việc từ bất cứ đâu có internet, thúc đẩy sự hợp tác liền mạch dù ở các múi giờ hay địa điểm khác nhau. Sẽ còn tuyệt vời hơn nữa nếu các công cụ này có khả năng mô phỏng, giúp chúng ta thấy được tác động của từng quyết định. Từ đó, chúng ta có thể dự đoán và tăng khả năng thành công. Chẳng hạn, các nhà nghiên cứu đã đề xuất một giải pháp với thuật toán sắp xếp chiplet sử dụng thông tin bản đồ nhiệt cho từng vị trí chiplet cụ thể. Họ dùng nó để tìm ra một bố cục giúp giảm thiểu tổng chiều dài dây dẫn và giữ nhiệt độ dưới ngưỡng cho phép. Trong một số thử nghiệm, nhóm đã đạt được mục tiêu chỉ trong chưa đầy 15 lần lặp. Họ xác nhận rằng phương pháp này giúp hội tụ nhanh hơn và hỗ trợ tối ưu hóa quy mô lớn. Vì công cụ này không yêu cầu huấn luyện thuật toán, nó triển khai nhanh hơn đáng kể so với một số lựa chọn khác. Chúng ta cũng có thể chỉ định các thông số như độ dẫn nhiệt và các nguồn nhiệt cụ thể, cũng như cách chúng ảnh hưởng đến vị trí từng chiplet để tìm ra lựa chọn tốt nhất. Những công cụ như thế này đang hỗ trợ rất nhiều cho việc ứng dụng phân tích dữ liệu ngày càng tăng để cải thiện quy trình sản xuất bán dẫn. Ngoài việc sử dụng các nền tảng chuyên biệt để xác định các vấn đề lớn, các nhà quản lý còn có thể đi sâu hơn để xác định khả năng các vấn đề quản lý nhiệt đang gây ra những lỗi đó.

Tóm lại, khi chip ngày càng nhỏ và phức tạp hơn, các hạn chế về hình học ngày càng trở thành yếu tố chính gây ra thách thức trong quản lý nhiệt. Các chuyên gia cần nhận diện và giải quyết những vấn đề dựa trên hình học này bằng các chiến lược có chủ đích và những phương pháp tốt nhất. Việc quản lý các thách thức nhiệt trong lắp ráp đa chip là vô cùng cần thiết, bởi vì kiến trúc 3D mang đến những ràng buộc hình học phức tạp. Các nhà thiết kế phải đặc biệt chú ý đến các yếu tố hình học này – như nhiệt cục bộ từ mật độ công suất không đều, luồng nhiệt dọc bị hạn chế và vị trí các thành phần có thể chặn các đường thoát nhiệt quan trọng – để duy trì quản lý nhiệt hiệu quả. Bằng cách sử dụng các công cụ mô phỏng tiên tiến và thuật toán thiết kế, chúng ta có thể dự đoán và giải quyết các thách thức quản lý nhiệt liên quan đến hình học, không còn phải mò mẫm thử và sai nữa, mà thay vào đó là đảm bảo hiệu suất tối ưu và độ tin cậy lâu dài cho sản phẩm.

Nguồn: EETimes