Dũng Đỗ

Writer

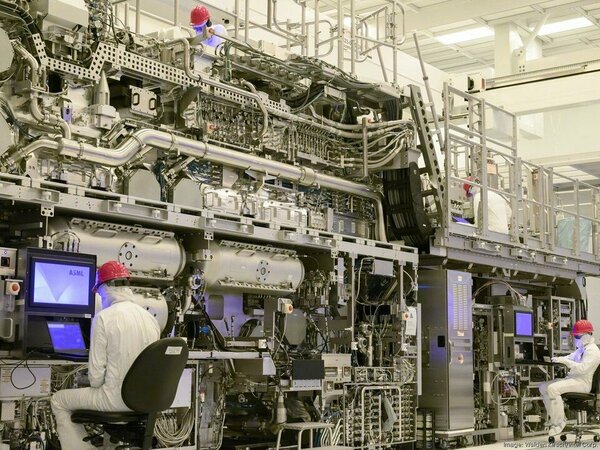

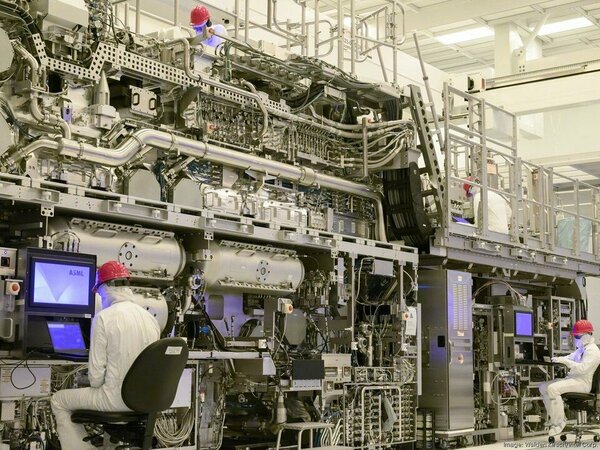

Tại sự kiện Intel Foundry Direct 2025 vừa diễn ra, Intel đã hé lộ một chiến lược đầy thận trọng đối với việc triển khai công nghệ quang khắc cực tím siêu cực đại khẩu độ cao (High-NA EUV) – thế hệ máy in chip tiên tiến và đắt đỏ nhất thế giới (~400 triệu USD/máy). Mặc dù là công ty đầu tiên trên thế giới nhận và lắp đặt thành công các hệ thống High-NA EUV này (từ ASML), Intel cho biết họ chưa cam kết sẽ sử dụng hoàn toàn công nghệ này cho việc sản xuất hàng loạt tiến trình 14A (tương đương 1.4nm) trong tương lai. Thay vào đó, hãng đang theo đuổi một cách tiếp cận song song, đầy tính toán để "giảm thiểu rủi ro" (de-risking).

Bài học từ thất bại 10nm

Quyết định dè dặt này của Intel được cho là xuất phát từ "vết sẹo" đau đớn của thất bại với tiến trình 10nm trước đây. Khi đó, việc Intel cố gắng tích hợp quá nhiều công nghệ mới chưa hoàn thiện vào cùng một nút quy trình đã dẫn đến sự chậm trễ kéo dài nhiều năm, khiến hãng mất vị thế dẫn đầu vào tay TSMC. Giờ đây, với High-NA EUV – một công nghệ vẫn còn nhiều yếu tố chưa ổn định từ vật liệu cản quang, mặt nạ quang học đến các thuật toán tính toán phức tạp – Intel không muốn lặp lại sai lầm đó.

Chiến lược "hai chân" cho 14A

Thay vì đặt cược tất cả vào High-NA EUV, Intel đang phát triển hai quy trình sản xuất song song cho nút 14A: một quy trình tiếp tục sử dụng máy Low-NA EUV (khẩu độ 0.33) hiện tại kết hợp với kỹ thuật đa mẫu phức tạp (triple-patterning), và một quy trình mới có tích hợp High-NA EUV. Điều quan trọng là cả hai quy trình này đều được thiết kế để tương thích với cùng một bộ quy tắc thiết kế (design rules), cho phép Intel linh hoạt chuyển đổi hoặc lựa chọn phương án tối ưu nhất khi tiến đến sản xuất hàng loạt mà không ảnh hưởng đến thiết kế của khách hàng.

Intel tự tin khẳng định cả hai quy trình hiện đều cho kết quả tương đương về tỷ lệ sản phẩm thành phẩm tốt (yield parity). Đây là một thành tựu đáng kể, cho thấy năng lực xử lý đa mẫu và xếp chồng lớp (overlay) trên quy trình Low-NA EUV của Intel đã được cải thiện rất nhiều.

High-NA EUV: Ưu và nhược điểm

Mặc dù có khả năng in khắc với độ phân giải cao hơn, High-NA EUV hiện tại vẫn còn một số hạn chế. Đáng kể nhất là việc nó chỉ in được một nửa diện tích mặt nạ (reticle) mỗi lần phơi sáng, đòi hỏi phải thực hiện hai lượt in và ghép lại đối với các con chip lớn, có thể ảnh hưởng đến năng suất tổng thể. Trong khi đó, Low-NA EUV vẫn có thể in toàn bộ mặt nạ trong một lần.

Tuy nhiên, Intel tin rằng về lâu dài, High-NA EUV sẽ giúp giảm thiểu số bước xử lý phức tạp cho các lớp (layer) quan trọng nhất trong con chip. Hãng đưa ra ví dụ một mẫu pattern nhất định nếu dùng High-NA chỉ cần một lượt in, trong khi dùng Low-NA cần tới ba lượt in và 40 bước xử lý khác. Việc tinh gọn này có thể giúp giảm chi phí sản xuất và cải thiện hiệu suất cho một số lớp nhất định trong chip 14A.

So sánh với đối thủ và lợi thế tiềm năng

Đáng chú ý, đối thủ lớn nhất của Intel là TSMC cũng đã tuyên bố sẽ không sử dụng High-NA EUV cho tiến trình A14 tương đương của họ (dự kiến ra mắt cùng thời điểm 2028), mà sẽ chờ đến phiên bản nâng cấp A14P sau đó (dự kiến sau 2029). Quyết định này cho thấy sự thận trọng chung của toàn ngành đối với chi phí và độ phức tạp của High-NA EUV.

Tuy nhiên, việc Intel tiên phong đầu tư và thử nghiệm sớm công nghệ này (đã xử lý hơn 30.000 wafer R&D bằng High-NA) có thể mang lại lợi thế về kinh nghiệm và khả năng làm chủ công nghệ. Nếu High-NA EUV chứng tỏ được hiệu quả và độ tin cậy trong sản xuất hàng loạt, Intel sẽ có bước đệm vững chắc để vượt lên trong cuộc đua công nghệ bán dẫn thế hệ tiếp theo. Chiến lược "hai chân" hiện tại cho phép Intel vừa thể hiện vai trò dẫn đầu công nghệ, vừa có phương án dự phòng an toàn nếu công nghệ mới chưa sẵn sàng.

Bài học từ thất bại 10nm

Quyết định dè dặt này của Intel được cho là xuất phát từ "vết sẹo" đau đớn của thất bại với tiến trình 10nm trước đây. Khi đó, việc Intel cố gắng tích hợp quá nhiều công nghệ mới chưa hoàn thiện vào cùng một nút quy trình đã dẫn đến sự chậm trễ kéo dài nhiều năm, khiến hãng mất vị thế dẫn đầu vào tay TSMC. Giờ đây, với High-NA EUV – một công nghệ vẫn còn nhiều yếu tố chưa ổn định từ vật liệu cản quang, mặt nạ quang học đến các thuật toán tính toán phức tạp – Intel không muốn lặp lại sai lầm đó.

Chiến lược "hai chân" cho 14A

Thay vì đặt cược tất cả vào High-NA EUV, Intel đang phát triển hai quy trình sản xuất song song cho nút 14A: một quy trình tiếp tục sử dụng máy Low-NA EUV (khẩu độ 0.33) hiện tại kết hợp với kỹ thuật đa mẫu phức tạp (triple-patterning), và một quy trình mới có tích hợp High-NA EUV. Điều quan trọng là cả hai quy trình này đều được thiết kế để tương thích với cùng một bộ quy tắc thiết kế (design rules), cho phép Intel linh hoạt chuyển đổi hoặc lựa chọn phương án tối ưu nhất khi tiến đến sản xuất hàng loạt mà không ảnh hưởng đến thiết kế của khách hàng.

Intel tự tin khẳng định cả hai quy trình hiện đều cho kết quả tương đương về tỷ lệ sản phẩm thành phẩm tốt (yield parity). Đây là một thành tựu đáng kể, cho thấy năng lực xử lý đa mẫu và xếp chồng lớp (overlay) trên quy trình Low-NA EUV của Intel đã được cải thiện rất nhiều.

High-NA EUV: Ưu và nhược điểm

Mặc dù có khả năng in khắc với độ phân giải cao hơn, High-NA EUV hiện tại vẫn còn một số hạn chế. Đáng kể nhất là việc nó chỉ in được một nửa diện tích mặt nạ (reticle) mỗi lần phơi sáng, đòi hỏi phải thực hiện hai lượt in và ghép lại đối với các con chip lớn, có thể ảnh hưởng đến năng suất tổng thể. Trong khi đó, Low-NA EUV vẫn có thể in toàn bộ mặt nạ trong một lần.

Tuy nhiên, Intel tin rằng về lâu dài, High-NA EUV sẽ giúp giảm thiểu số bước xử lý phức tạp cho các lớp (layer) quan trọng nhất trong con chip. Hãng đưa ra ví dụ một mẫu pattern nhất định nếu dùng High-NA chỉ cần một lượt in, trong khi dùng Low-NA cần tới ba lượt in và 40 bước xử lý khác. Việc tinh gọn này có thể giúp giảm chi phí sản xuất và cải thiện hiệu suất cho một số lớp nhất định trong chip 14A.

So sánh với đối thủ và lợi thế tiềm năng

Đáng chú ý, đối thủ lớn nhất của Intel là TSMC cũng đã tuyên bố sẽ không sử dụng High-NA EUV cho tiến trình A14 tương đương của họ (dự kiến ra mắt cùng thời điểm 2028), mà sẽ chờ đến phiên bản nâng cấp A14P sau đó (dự kiến sau 2029). Quyết định này cho thấy sự thận trọng chung của toàn ngành đối với chi phí và độ phức tạp của High-NA EUV.

Tuy nhiên, việc Intel tiên phong đầu tư và thử nghiệm sớm công nghệ này (đã xử lý hơn 30.000 wafer R&D bằng High-NA) có thể mang lại lợi thế về kinh nghiệm và khả năng làm chủ công nghệ. Nếu High-NA EUV chứng tỏ được hiệu quả và độ tin cậy trong sản xuất hàng loạt, Intel sẽ có bước đệm vững chắc để vượt lên trong cuộc đua công nghệ bán dẫn thế hệ tiếp theo. Chiến lược "hai chân" hiện tại cho phép Intel vừa thể hiện vai trò dẫn đầu công nghệ, vừa có phương án dự phòng an toàn nếu công nghệ mới chưa sẵn sàng.