Thế Việt

Writer

Phân tích die shot từ Geekerwan hé lộ chip 3nm "cây nhà lá vườn" đầu tiên của Xiaomi có kích thước đế nhỏ nhất so với Snapdragon 8 Elite, Dimensity 9400 và A18 Pro, nhưng lại sở hữu lượng cache L2, L3 "khủng" cho từng cụm CPU, GPU, NPU. Đây có phải là chiến lược thông minh để cân bằng giữa chi phí, hiệu năng và điện năng tiêu thụ?

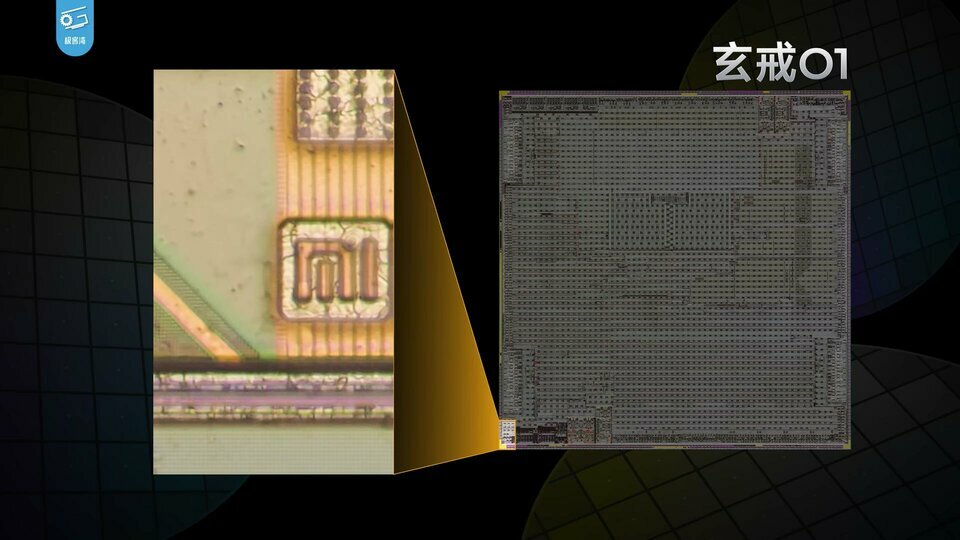

Con Chip Xring O1 được Xiaomi khắc hẳn logo của hãng trên die chip

XRing O1: Thiết kế "dị" nhưng đầy tính toán của Xiaomi

Khi các chuyên gia công nghệ đặt con chip XRING O1 mới nhất của Xiaomi dưới kính hiển vi để phân tích chi tiết cấu trúc bên trong (die shot), họ đã có một phát hiện đầy bất ngờ. Chiếc chip tự thiết kế thương mại đầu tiên trên tiến trình 3nm của "gã khổng lồ" công nghệ Trung Quốc này thiếu vắng một thành phần mà hầu hết các dòng chip flagship khác trên thị trường đều có: SLC cache (System Level Cache – Bộ nhớ đệm cấp hệ thống).

Tuy nhiên, thay vì coi đây là một "thiếu sót" hay một sự cắt giảm để tiết kiệm chi phí đơn thuần, các kỹ sư của Xiaomi dường như đã biến việc loại bỏ SLC cache thành một phần trong một chiến lược thiết kế thông minh và đầy chủ ý.

Trong thế giới chip di động phức tạp, SLC cache thường được coi như một thành phần quan trọng, đóng vai trò như một "trung tâm giao thông" giúp các khối chức năng khác nhau bên trong con chip (như CPU, GPU, NPU) có thể "trò chuyện" và trao đổi dữ liệu với nhau một cách hiệu quả và nhanh chóng hơn. Dù vậy, đội ngũ kỹ sư tài năng của Xiaomi, đứng sau dự án XRing O1, đã có một cách nhìn và một hướng tiếp cận khác biệt về vấn đề này.

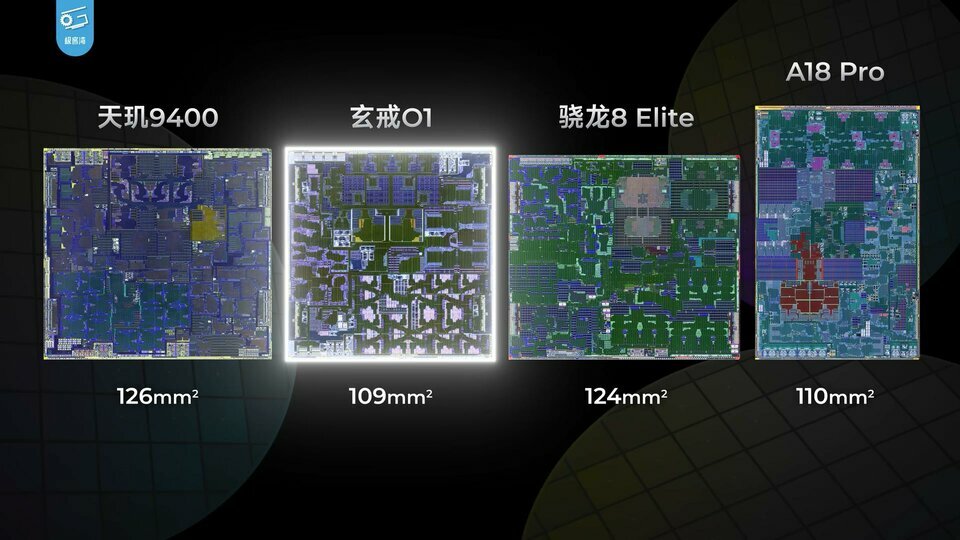

Die size nhỏ nhất, cache riêng "khủng" cho từng thành phần

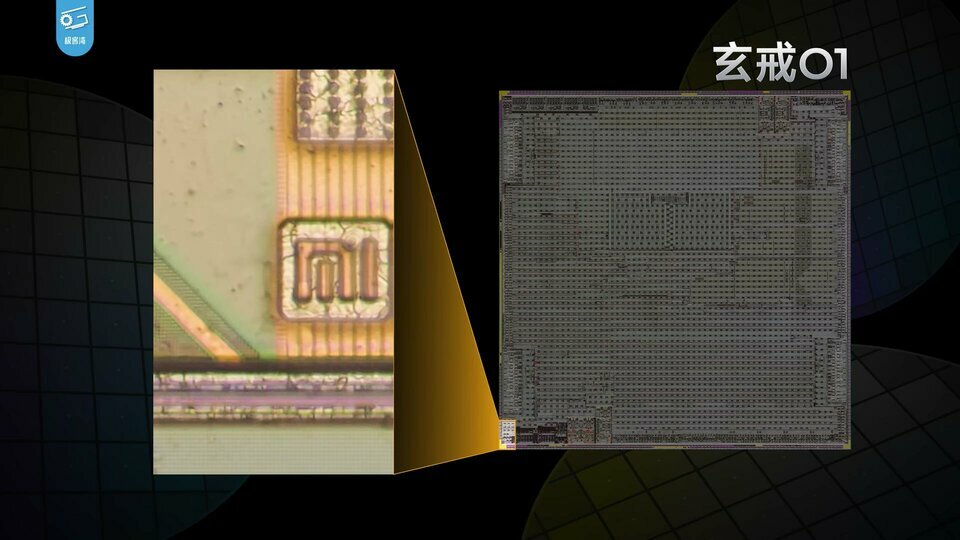

Phân tích chi tiết từ kênh YouTube công nghệ uy tín Geekerwan cho thấy, XRING O1 được sản xuất trên quy trình 3nm thế hệ thứ hai của TSMC (N3E). Nhưng điều đặc biệt hơn là nó có kích thước đế (die size) nhỏ nhất khi so sánh với tất cả các đối thủ cùng thế hệ như Snapdragon 8 Elite của Qualcomm, Dimensity 9400 của MediaTek hay A18 Pro của Apple. Việc giữ cho kích thước đế nhỏ gọn không chỉ giúp Xiaomi giảm thiểu chi phí sản xuất trên mỗi con chip mà còn buộc họ phải tối ưu hóa từng milimét vuông trên đế chip một cách hiệu quả nhất.

Cùng sử dụng tiến trình 3nm, nhưng die chip Xring của Xiaomi có kích thước nhỏ nhất so với Snapdragon 8 Elite, Dimensity 9400 và A18 Pro

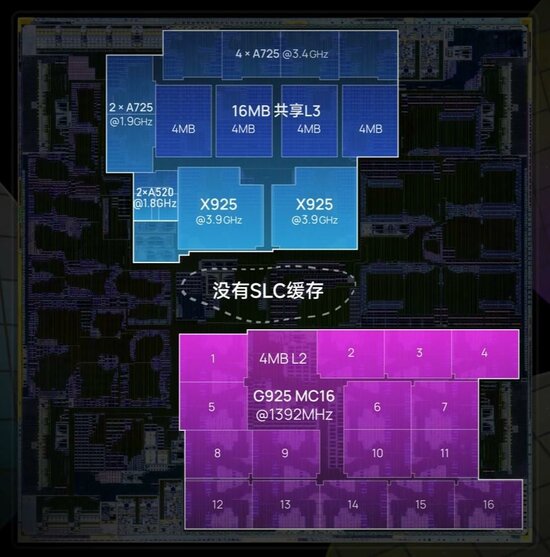

Thay vì dành một phần không gian quý giá trên đế chip cho SLC cache, Xiaomi đã đưa ra một quyết định có phần táo bạo: tăng cường dung lượng bộ nhớ đệm (cache) cho từng thành phần xử lý riêng lẻ.

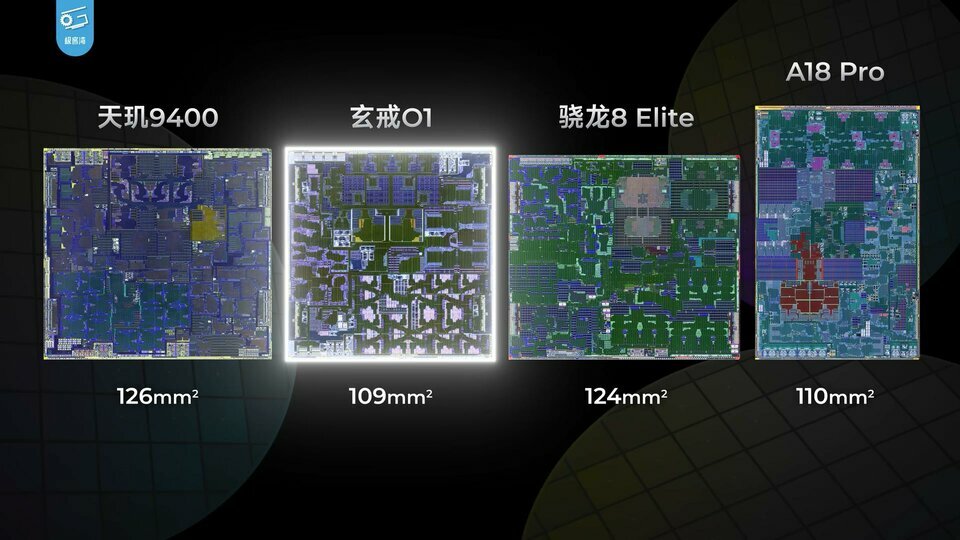

Cách phân bổ bộ nhớ đệm trên 10 nhân CPU của Xiaomi Xring

Tại sao Xiaomi "dám" bỏ SLC cache?

Lý do đằng sau quyết định có phần "khác người" này không hoàn toàn xuất phát từ những hạn chế về mặt kỹ thuật, mà được cho là đến từ một sự hiểu biết sâu sắc về cách thức hoạt động của chip trong các tình huống sử dụng thực tế. Các kỹ sư của Xiaomi dường như đã nhận ra rằng SLC cache, dù có vai trò nhất định, đôi khi lại có thể trở thành một "gánh nặng", đặc biệt là trong các tác vụ nhẹ nhàng hàng ngày. Khi con chip không cần phải xử lý những công việc nặng nhọc, việc duy trì hoạt động của SLC cache có thể làm tăng mức tiêu thụ điện năng một cách không cần thiết, ảnh hưởng đến thời lượng pin của thiết bị.

Một chuyên gia phân tích trong ngành đã giải thích rằng SLC cache chỉ thực sự phát huy tác dụng tối đa khi cần truyền tải một lượng lớn dữ liệu giữa các khối chức năng khác nhau trong chip, ví dụ như giữa CPU và GPU, hoặc giữa NPU và CPU. Tuy nhiên, trong thực tế, do kích thước thường nhỏ hơn đáng kể so với L3 cache, SLC cache lại thường có tỷ lệ bỏ lỡ cache (miss cache rate) khá cao và có thể vô tình tạo ra độ trễ không mong muốn khi hệ thống phải truy cập vào bộ nhớ chính. Thay vì luôn cải thiện hiệu suất, SLC cache đôi khi lại có thể mang đến tác động tiêu cực, đặc biệt là việc tạo thêm một lớp kiểm tra dữ liệu không thực sự cần thiết trước khi cho phép truy cập vào bộ nhớ chính (RAM).

Bộ nhớ đệm trên GPU của Xiaomi Xring

Hiệu năng thực tế và những câu hỏi còn bỏ ngỏ

Chiến lược thiết kế độc đáo này của Xiaomi dường như đã phần nào mang lại thành công. Kết quả từ bài kiểm tra Geekbench 6 cho thấy XRING O1 hoàn toàn có thể cạnh tranh sòng phẳng với Snapdragon 8 Elite trong bài test đa nhân (multi-core), chỉ chậm hơn một chút không đáng kể. Đây là một thành tích rất đáng nể, đặc biệt khi xem xét rằng đây mới chỉ là con chip flagship tự thiết kế đầu tiên của Xiaomi được thương mại hóa, trong khi Qualcomm đã có hàng thập kỷ kinh nghiệm trong lĩnh vực này.

Tuy nhiên, không phải mọi thứ đều hoàn hảo. Khi các chuyên gia độc lập tiến hành các bài kiểm tra hiệu năng tổng thể bằng AnTuTu Benchmark, họ phát hiện ra rằng XRING O1 chỉ đạt được điểm số thấp hơn khoảng 13% so với con số 3 triệu điểm mà Xiaomi từng công bố trước đó. Điều này đang đặt ra một câu hỏi lớn: liệu việc thiếu vắng SLC cache có phải là một trong những nguyên nhân chính gây ra sự chênh lệch này hay không, đặc biệt là trong các tác vụ đòi hỏi sự phối hợp chặt chẽ giữa nhiều khối xử lý.

Bộ nhớ SLC - thành phần thường thấy trên các chip flagship khác - đã không xuất hiện trên chip của Xiaomi

Mặc dù vậy, ngay cả với những hạn chế nhất định, điểm số của XRING O1 vẫn được đánh giá là vượt trội hơn hẳn so với các dòng chip tự thiết kế khác trên thị trường như Google Tensor hay Huawei Kirin (theo nhận định trong video của Geekerwan). Điều này cho thấy Xiaomi đã có một khởi đầu rất ấn tượng trong cuộc đua tự phát triển chip di động, một lĩnh vực mà trước đây chỉ có những "ông lớn" thực sự như Apple, Samsung hay Google mới dám dấn thân vào.

Việc Xiaomi lựa chọn cấu hình CPU 10 nhân thay vì 8 nhân như thông thường cũng là một quyết định thú vị. Có vẻ như các kỹ sư của hãng đã nhận ra rằng thay vì chỉ tập trung vào việc tăng tốc độ xung nhịp của từng nhân riêng lẻ (điều này thường đi kèm với việc tăng tiêu thụ điện năng và tỏa nhiệt), việc có thêm hai nhân xử lý có thể mang lại hiệu quả tốt hơn trong các tác vụ đa luồng, đồng thời giúp phân tán tải công việc một cách hiệu quả hơn, từ đó tối ưu hóa cả hiệu năng lẫn khả năng tiết kiệm pin.

#ChipXiaomiXringO1

Con Chip Xring O1 được Xiaomi khắc hẳn logo của hãng trên die chip

XRing O1: Thiết kế "dị" nhưng đầy tính toán của Xiaomi

Khi các chuyên gia công nghệ đặt con chip XRING O1 mới nhất của Xiaomi dưới kính hiển vi để phân tích chi tiết cấu trúc bên trong (die shot), họ đã có một phát hiện đầy bất ngờ. Chiếc chip tự thiết kế thương mại đầu tiên trên tiến trình 3nm của "gã khổng lồ" công nghệ Trung Quốc này thiếu vắng một thành phần mà hầu hết các dòng chip flagship khác trên thị trường đều có: SLC cache (System Level Cache – Bộ nhớ đệm cấp hệ thống).

Tuy nhiên, thay vì coi đây là một "thiếu sót" hay một sự cắt giảm để tiết kiệm chi phí đơn thuần, các kỹ sư của Xiaomi dường như đã biến việc loại bỏ SLC cache thành một phần trong một chiến lược thiết kế thông minh và đầy chủ ý.

Trong thế giới chip di động phức tạp, SLC cache thường được coi như một thành phần quan trọng, đóng vai trò như một "trung tâm giao thông" giúp các khối chức năng khác nhau bên trong con chip (như CPU, GPU, NPU) có thể "trò chuyện" và trao đổi dữ liệu với nhau một cách hiệu quả và nhanh chóng hơn. Dù vậy, đội ngũ kỹ sư tài năng của Xiaomi, đứng sau dự án XRing O1, đã có một cách nhìn và một hướng tiếp cận khác biệt về vấn đề này.

Die size nhỏ nhất, cache riêng "khủng" cho từng thành phần

Phân tích chi tiết từ kênh YouTube công nghệ uy tín Geekerwan cho thấy, XRING O1 được sản xuất trên quy trình 3nm thế hệ thứ hai của TSMC (N3E). Nhưng điều đặc biệt hơn là nó có kích thước đế (die size) nhỏ nhất khi so sánh với tất cả các đối thủ cùng thế hệ như Snapdragon 8 Elite của Qualcomm, Dimensity 9400 của MediaTek hay A18 Pro của Apple. Việc giữ cho kích thước đế nhỏ gọn không chỉ giúp Xiaomi giảm thiểu chi phí sản xuất trên mỗi con chip mà còn buộc họ phải tối ưu hóa từng milimét vuông trên đế chip một cách hiệu quả nhất.

Cùng sử dụng tiến trình 3nm, nhưng die chip Xring của Xiaomi có kích thước nhỏ nhất so với Snapdragon 8 Elite, Dimensity 9400 và A18 Pro

Thay vì dành một phần không gian quý giá trên đế chip cho SLC cache, Xiaomi đã đưa ra một quyết định có phần táo bạo: tăng cường dung lượng bộ nhớ đệm (cache) cho từng thành phần xử lý riêng lẻ.

- CPU 10 nhân: Được trang bị tới 16MB L3 cache – một con số khá ấn tượng trong thế giới chip di động. Mỗi nhân siêu hiệu năng Cortex-X925 cao cấp nhất được phân bổ 2MB L2 cache, trong khi các nhân hiệu năng cao Cortex-A725 có 1MB L2 cache và các nhân tiết kiệm điện Cortex-A520 được chia sẻ 512KB L2 cache.

- GPU 16 nhân ARM Immortalis-G925: Cũng không hề bị "cắt giảm" khi được trang bị 4MB L2 cache.

- NPU 6 nhân tự thiết kế: Thậm chí còn "hào phóng" hơn với 10MB cache chuyên dụng.

Cách phân bổ bộ nhớ đệm trên 10 nhân CPU của Xiaomi Xring

Tại sao Xiaomi "dám" bỏ SLC cache?

Lý do đằng sau quyết định có phần "khác người" này không hoàn toàn xuất phát từ những hạn chế về mặt kỹ thuật, mà được cho là đến từ một sự hiểu biết sâu sắc về cách thức hoạt động của chip trong các tình huống sử dụng thực tế. Các kỹ sư của Xiaomi dường như đã nhận ra rằng SLC cache, dù có vai trò nhất định, đôi khi lại có thể trở thành một "gánh nặng", đặc biệt là trong các tác vụ nhẹ nhàng hàng ngày. Khi con chip không cần phải xử lý những công việc nặng nhọc, việc duy trì hoạt động của SLC cache có thể làm tăng mức tiêu thụ điện năng một cách không cần thiết, ảnh hưởng đến thời lượng pin của thiết bị.

Một chuyên gia phân tích trong ngành đã giải thích rằng SLC cache chỉ thực sự phát huy tác dụng tối đa khi cần truyền tải một lượng lớn dữ liệu giữa các khối chức năng khác nhau trong chip, ví dụ như giữa CPU và GPU, hoặc giữa NPU và CPU. Tuy nhiên, trong thực tế, do kích thước thường nhỏ hơn đáng kể so với L3 cache, SLC cache lại thường có tỷ lệ bỏ lỡ cache (miss cache rate) khá cao và có thể vô tình tạo ra độ trễ không mong muốn khi hệ thống phải truy cập vào bộ nhớ chính. Thay vì luôn cải thiện hiệu suất, SLC cache đôi khi lại có thể mang đến tác động tiêu cực, đặc biệt là việc tạo thêm một lớp kiểm tra dữ liệu không thực sự cần thiết trước khi cho phép truy cập vào bộ nhớ chính (RAM).

Bộ nhớ đệm trên GPU của Xiaomi Xring

Hiệu năng thực tế và những câu hỏi còn bỏ ngỏ

Chiến lược thiết kế độc đáo này của Xiaomi dường như đã phần nào mang lại thành công. Kết quả từ bài kiểm tra Geekbench 6 cho thấy XRING O1 hoàn toàn có thể cạnh tranh sòng phẳng với Snapdragon 8 Elite trong bài test đa nhân (multi-core), chỉ chậm hơn một chút không đáng kể. Đây là một thành tích rất đáng nể, đặc biệt khi xem xét rằng đây mới chỉ là con chip flagship tự thiết kế đầu tiên của Xiaomi được thương mại hóa, trong khi Qualcomm đã có hàng thập kỷ kinh nghiệm trong lĩnh vực này.

Tuy nhiên, không phải mọi thứ đều hoàn hảo. Khi các chuyên gia độc lập tiến hành các bài kiểm tra hiệu năng tổng thể bằng AnTuTu Benchmark, họ phát hiện ra rằng XRING O1 chỉ đạt được điểm số thấp hơn khoảng 13% so với con số 3 triệu điểm mà Xiaomi từng công bố trước đó. Điều này đang đặt ra một câu hỏi lớn: liệu việc thiếu vắng SLC cache có phải là một trong những nguyên nhân chính gây ra sự chênh lệch này hay không, đặc biệt là trong các tác vụ đòi hỏi sự phối hợp chặt chẽ giữa nhiều khối xử lý.

Bộ nhớ SLC - thành phần thường thấy trên các chip flagship khác - đã không xuất hiện trên chip của Xiaomi

Mặc dù vậy, ngay cả với những hạn chế nhất định, điểm số của XRING O1 vẫn được đánh giá là vượt trội hơn hẳn so với các dòng chip tự thiết kế khác trên thị trường như Google Tensor hay Huawei Kirin (theo nhận định trong video của Geekerwan). Điều này cho thấy Xiaomi đã có một khởi đầu rất ấn tượng trong cuộc đua tự phát triển chip di động, một lĩnh vực mà trước đây chỉ có những "ông lớn" thực sự như Apple, Samsung hay Google mới dám dấn thân vào.

Việc Xiaomi lựa chọn cấu hình CPU 10 nhân thay vì 8 nhân như thông thường cũng là một quyết định thú vị. Có vẻ như các kỹ sư của hãng đã nhận ra rằng thay vì chỉ tập trung vào việc tăng tốc độ xung nhịp của từng nhân riêng lẻ (điều này thường đi kèm với việc tăng tiêu thụ điện năng và tỏa nhiệt), việc có thêm hai nhân xử lý có thể mang lại hiệu quả tốt hơn trong các tác vụ đa luồng, đồng thời giúp phân tán tải công việc một cách hiệu quả hơn, từ đó tối ưu hóa cả hiệu năng lẫn khả năng tiết kiệm pin.

#ChipXiaomiXringO1